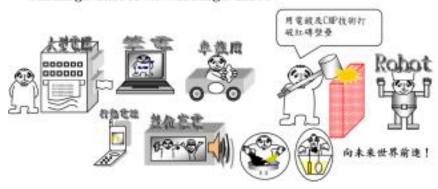

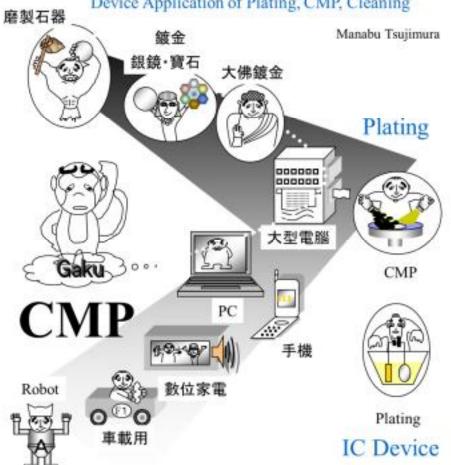

Device Application of Plating, CMP, Cleaning

精密機械公司成立於1985年。

最初是從荏原製作所的一項企業專案開始跨入精密機械領域。 展為事業部再升格成為公司。一直延續發展至今。 今年、2025年是精密機械公司成立40周年紀念。為此。 我想要將我的拙著呈現給各位關照過我的朋友們。 希望能對您有所幫助。

2025年5月1日 荏原製作所公司 研究員 辻村學

Copyright for these works is reserved to the authors. Downloading files is free, but reprinting or reproducing the content requires the author's permission.

今年(2007年)2月,D教授對我說:「辻村君,這些內容很有趣呢,別只是給學生用,請你 務必出版呀! 」。

這本被稱為 "有趣" 的書, 是我集結過去 20 多年的經驗寫給學生用的教科書。我在 1985 年 進入半導體的世界, 自此之後便一心投入半導體製造裝置和組件的開發工作。2002年, 我在首都 大學東京的太田教授指導下,取得學位。從1997年以來,我便和美國克拉克森大學的鮑伯教授 一起研究 CMP, 想不到取得學位後便收到他詢問我當客座教授的意願。就在我為生活忙碌時, 也 收到了來自首都大學東京,以及韓國漢陽大學的圤教授關於客座教授的徵詢,現在我在日、美、 韓三國執教鞭,教導半導體裝置,展開一場 Wet Revolution (濕式革命)。本書便是由課堂講義 中選取出來的内容。

我任職了32年的荏原製作所,也實施或指導半導體的開發工作。本書是我從工作的經驗中, 擷取如何處理研磨、鍍金等半導體設備製程所用的濕式製程之綜合說明書,同時也請各位把這本 書想成是一本開發用的參考指南。本書的適用對象包含兩種人,對於在大學裡研究這些製程或裝 置的人,本書可以當作教科書使用;對於已經在企業裡專門負責開發的研究人員,本書可以提供 先進的資訊。希望讀者們能分別讀取自己想要的資訊。

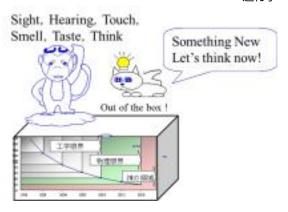

我深信科學(Science)與技術(Technology)是經過「99%的模仿與 1%的 Something New」 進化而來的。單純的模仿雖然很不長進,但如果能在前人的辛苦上加以進化 (Evolution)、革新 (Innovation)、 甚而革命 (Revolution) 的話, 那麼一開始直接從模仿下手也很好。 當模仿的階 段結束以後,就要賭上工程師的榮譽,創造新的技術。本書雖然有99%的內容重覆了前人辛苦得 來的成果,不過我相信書中也可以為各位介紹 1%的 Something New。我誠摯地希望讀完本書的 人能給我評價。至今為止,我們公司裡受到我嚴厲批評的工程師和學生們滿懷怨恨的評價,都令 人感到很困擾呀 (笑)。

能夠完成本書,我非常感謝東芝股份有限公司的柴田英毅和小寺雅子兩位提供珍貴的資料。 此外,對於2002年指導我完成學位的首都大學東京的太田教授,以及最初任用我為客座教授的

©2025Manabu Tsujimura. All rights reserved.

對了,本書之所以能夠寫得這麼"有趣"(我自己也這麼覺得),其實都要歸功學生的幫忙。 克拉克森大學的學生丟給我各式各樣的問題,這些全都成為開發工作的材料,也成了本書的材料。 每年來我這裡實習 1~2 個月的漢陽大學學生 (3~4 名) 也相當熱心, 讓我學到很多東西。另外, 首都大學東京的學生也給予我協助,參與了本書「Bell Best Project」的角色模擬實驗。我把在企 業裡學會的事物教給學生,也從學生身上學習,就這樣教學相長完成了本書。

當然,對於敝公司工程師的日夜關照,我理應稱謝,此外還有和我來往的設備商、材料商、 投資人分析師...等等, 我得到數不盡的貴人幫忙才能完成本書。

再來我要對促成本書出版的土肥教授,以及為本書出版貢獻心力的工業調查會致上深深的謝 意。

啊!不好了,我還得對最麻煩到她、最照顧我的愛妻久美子(在本書中也有出場)道謝...。 2007年11月

辻村學

| • | 溫故知新                  |

|---|-----------------------|

|   | 世界最古老的技術: 電鍍與研磨8      |

|   | 來自克拉克森的問候12           |

| • | 平坦化頌歌                 |

|   | Planarization Carol12 |

|   | 精靈出現14                |

|   | 現在、古代、未來16            |

|   | СМР化為永恆18             |

| • | Bell Best Project     |

|   | "X" 計畫? 20            |

|   | 原子小金剛終於誕生?22          |

|   | 弱肉強食食物鏈24             |

|   | 推動專案                  |

|   | 擬定產品藍圖28              |

|   | 何謂 E G?30             |

|   | 了解晶片                  |

|   | Bell Boy 完成!          |

| 第 | l 篇 濕式成膜製程:電鍍 Plating |

目錄

# 半導體製程中電鍍扮演的角色?

| <b>火をなりた。                                    </b> | 20 |

|---------------------------------------------------|----|

| 從水桶到半導體電鍍                                         | 38 |

| 從舊3K到新3K                                          | 40 |

| 各種電鍍設備                                            | 42 |

| 四個應用                                              | 44 |

| 六個子系統                                             | 46 |

| 從法拉第定律開始吧                                         | 48 |

| 三個密藥                                              | 50 |

| 半導體製程所要求的電鍍性能                                     | 52 |

| 洗淨與汙染控制                                           | 54 |

| 實際應用例                                             |    |

| 在微細尺度下嵌入pinch off孔?                               | 56 |

只有60cc大的電鍍槽? ......58

|   | 浸漬材料對降低Terminal effect很有效       | 61  |

|---|---------------------------------|-----|

|   | 刺蝟製程                            | 62  |

|   | 高熔點金屬封蓋電鍍                       | 64  |

|   | 凸塊電鍍                            | 66  |

| 第 | III 篇 濕式削膜製程: 化學機械研磨製程 CMP      |     |

| • | 半導體製造製程中研磨 (CMP) 扮演的角色是?        |     |

|   | 從石頭(石器)到石頭(晶片)                  | 72  |

|   | Dryin,Dryout登場                  |     |

|   | CMP是毒品?!                        | 76  |

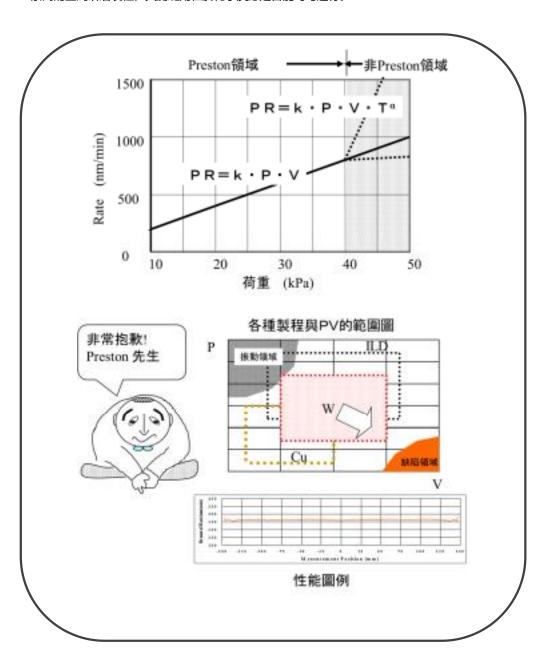

|   | 從 Preston 開始吧                   | 78  |

|   | 這就是研磨!                          | 80  |

|   | 奇怪!違反 Preston 算式?               | 82  |

|   | 傳授研磨的精髓吧                        |     |

|   | 永遠的課題:Paraten依存性 (Pattern Depen | •   |

|   | 用在晶片的哪裡?                        |     |

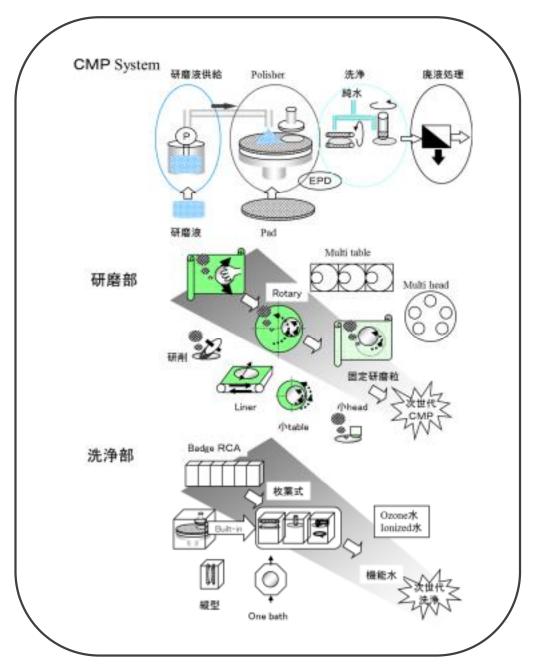

|   | 研磨部、洗淨部                         |     |

|   | 監控部                             |     |

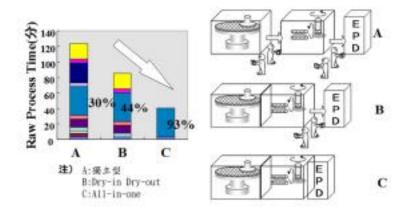

|   | Raw Process Time                |     |

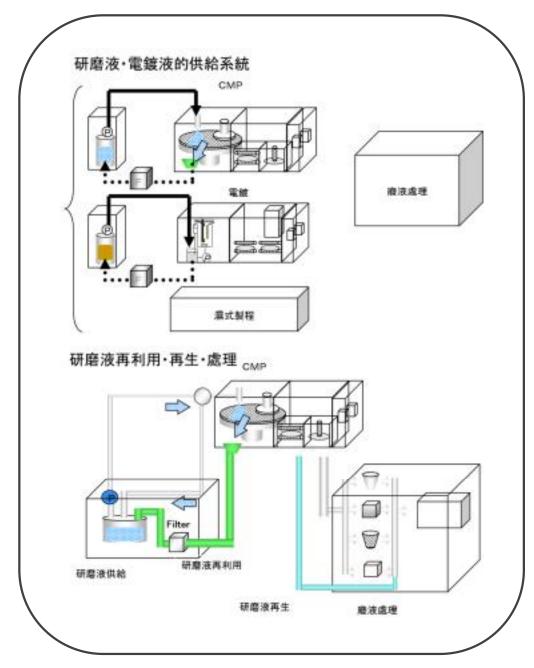

|   | 研磨液再生與廢液處理                      | 96  |

| • | 實際應用例                           |     |

|   | 從 ILD 層間絕緣膜開始                   | 98  |

|   | 以輪廓控制達到均一性                      | 100 |

|   | 從後面、從旁邊、轉圈圈                     | 102 |

|   | Dressing、流量與振動                  | 104 |

|   | 這就是 ILD 規格                      | 106 |

|   | STI CMP                         | 108 |

|   | 各種 STI 攻略法                      | 110 |

|   | W CMP                           | 112 |

|   | Cu 殘留是來自下層的 W?                  | 114 |

|   | 銅配線 CMP                         | 116 |

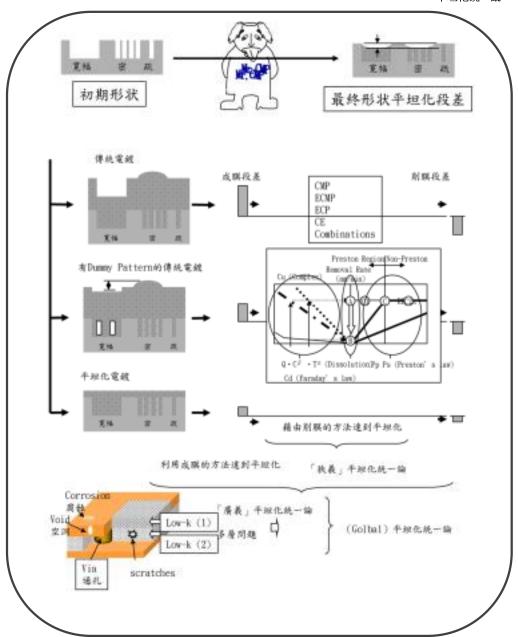

|   | 平坦化統一論                          | 118 |

|   | 低、再低、要那麼低?                      |     |

|   |                                 |     |

有限元素分析法在這裡也用得上 ......60

|   | 那就以分析進行實証122                            |

|---|-----------------------------------------|

|   | 各種加工方法                                  |

|   | CMP / ECMP / ECP / CE:這是什麼? 126         |

|   | 「狹義」平坦化統一論128                           |

|   | 「廣義」平坦化統一論130                           |

| • | 特殊開發例                                   |

|   | 奈米形貌(Nanotopography):STI 良率惡化!          |

|   | 竟然不沿著起伏研磨!                              |

|   | Roll-Off: 邊緣垂下136                       |

|   | 以邊緣 1mm 為目標138                          |

|   | FEM,從公里到奈米140                           |

|   | 來確認鑲嵌強度吧142                             |

| 第 | Ⅳ 篇 濕式表面改質製程: 洗淨與乾燥 Cleaning and Drying |

|   |                                         |

| • | 半導體製程的洗淨                                |

|   | 洗淨是戰場                                   |

|   | 要清什麼? 怎麼清才乾淨                            |

| • | 實際應用例                                   |

|   | 要洗得乾淨就要使用乾淨的裝置150                       |

|   | 讓環境更乾淨吧152                              |

|   | 引頸企盼的非接觸洗淨154                           |

|   | 馴服野馬156                                 |

| • | 半導體的乾燥                                  |

|   | 難以乾燥的材料就用IPA158                         |

|   | 好厲害! 疏水膜也輕鬆處理!                          |

| 第 | V篇 濕式製程應用: 這就是多層問題的全貌                   |

| • |                                         |

| • | 超高樓大廈與多層問題                              |

|   | Low-k 起司? Low-k 材料                      |

|   | 加溫起司: 固化                                |

|   | 개예(2년) - 변10 100                        |

©2025Manabu Tsujimura. All rights reserved.

|   | 漏電!沒辦法安心居住:可靠性               |

|---|------------------------------|

| • | Seven See's                  |

|   | 七個課題與七個解法 176                |

|   | 1'st See Direct CMP          |

|   | 2'nd See: CMP 低壓化要求: mC2 是什麼 |

|   | 3'rd See 釕阻隔膜182             |

|   | 4' th See: 無水痕要求184          |

|   | 5'th See: 1/2 CD雜質大小186      |

|   | 6'th See: 金屬蓋188             |

|   | 7'th See: 邊緣排除190            |

| • | Stand-By-Me                  |

|   | Stand-By-Me192               |

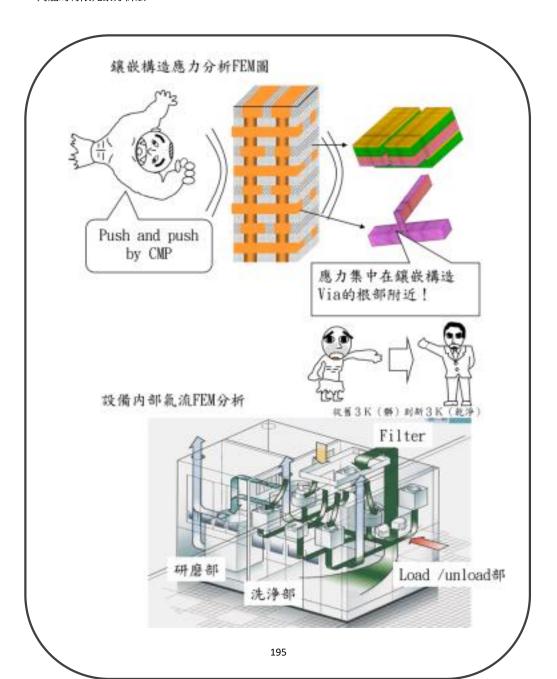

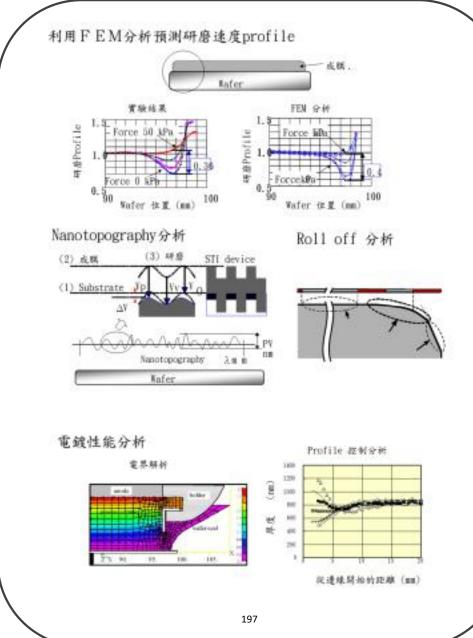

|   | 萬能的有限元素分析法194                |

|   | 電鍍與 CMP 的 FEM 運用196          |

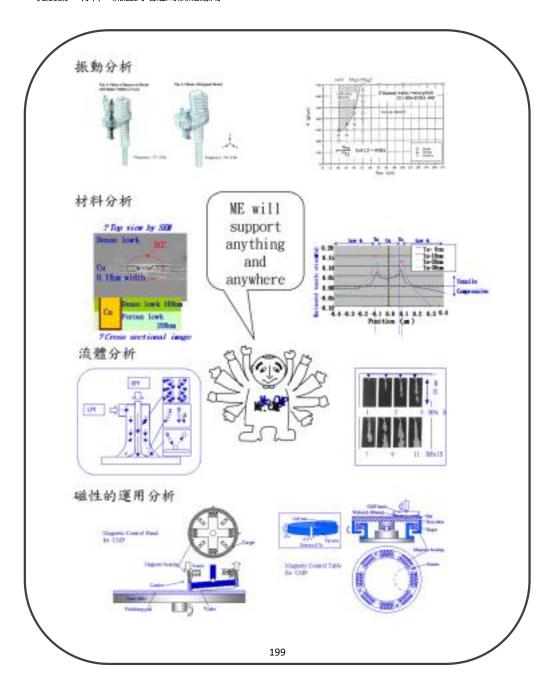

|   | 從震動、材料、流體到電磁的廣泛應用198         |

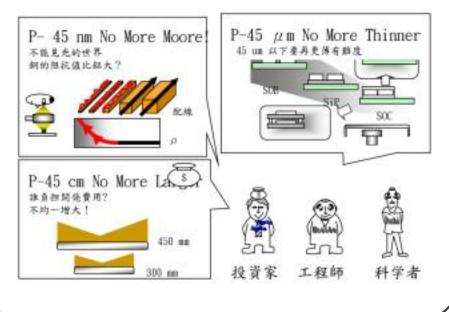

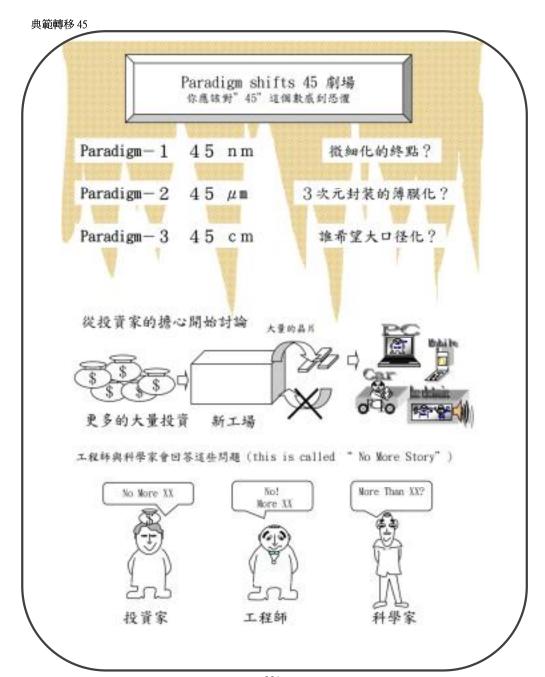

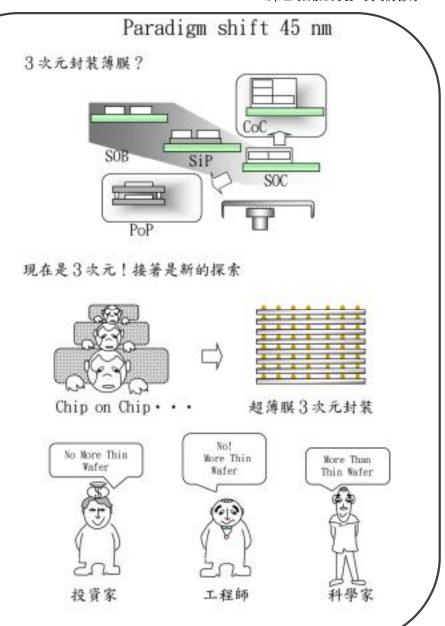

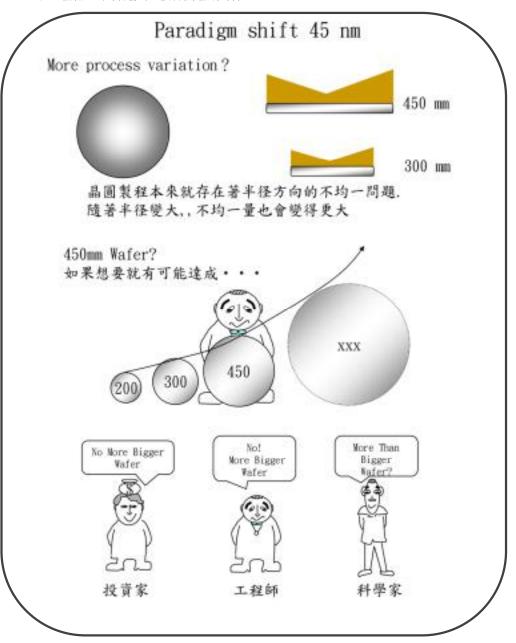

| • | 典範轉移 45                      |

|   | 典範轉移 4 5                     |

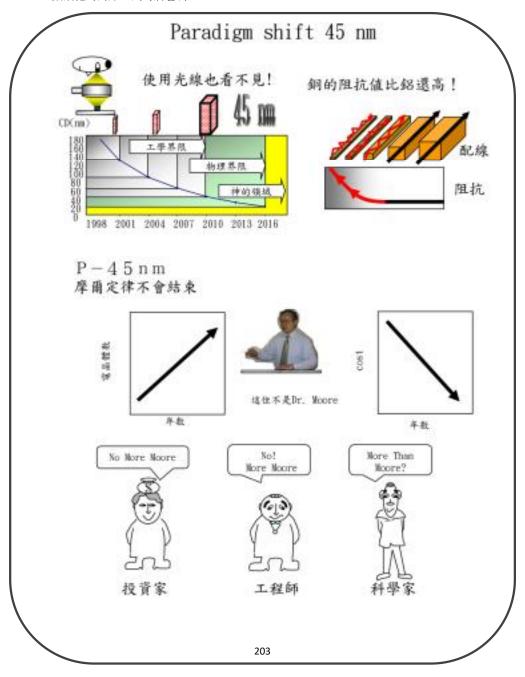

|   | 45nm 微細化的終點, 到時將會有202        |

|   | 45μm 採用 3D 封裝,到時將會有          |

|   | 45cm 大口徑化,到時將會有接著就是典範轉移      |

# 第I篇

# 平坦化頌歌

# **Planarization Carol**

溫故知新 世界最古老的技術:電鍍與研磨

# 世界最古老的技術: 電鍍與研磨

••••••

溫故知新 (溫習舊的知識,得到新的理解和體會:論語)

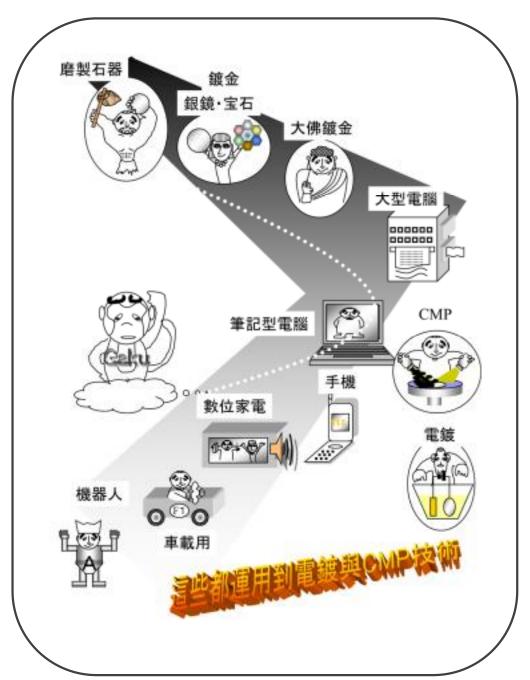

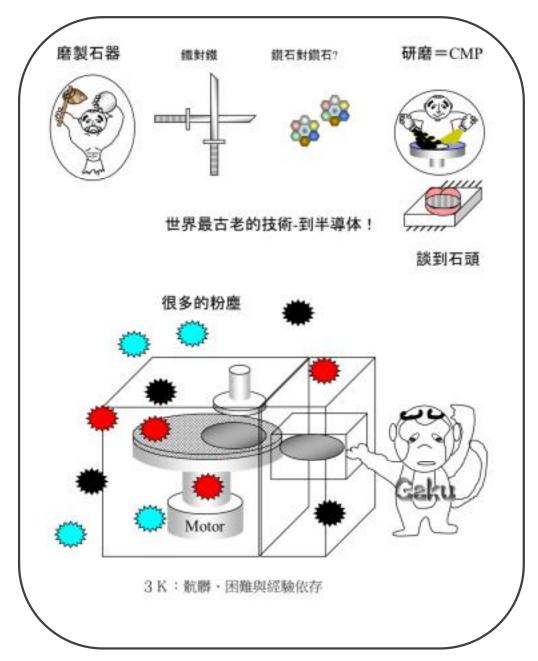

用來描述半導體裝置製造用的電鍍與研磨技術時,沒有任何一句話比它更加貼切了。磨製石器用的研磨技術,與製造奈良大佛的電鍍技術,對於當今最先進的半導體裝置製造而言,是不可或缺的技術。實際上,其基本原理自古以來完全沒變。只是施以研磨與電鍍的物品,變成「奈米等級」而已。本書的目的,就是要介紹這些既古老又新穎的技術。

### 電鍍與研磨應用在半導體上?

1980 年代,IBM 研發出了令人驚訝的技術。該公司將他人避之唯恐不及的銅,而且還是屬於所謂又髒、又辛苦、又需要經驗的 3K 產業,把電鍍與研磨技術應用到半導體裝置上! 現在如果不採用這種電鍍與研磨技術,就沒有辦法製造最先進的裝置。但是,當時又有誰能想像得到呢?坦白說吧。我是從 1987 年開始做電鍍、1989 年開始做研磨的,但是我當時完全不信這一套。然而,隨著時間過去,我開始覺得:「哎呀!這技術搞不好有用...」為什麼?讀者只要閱讀這本書,慢慢就會明白理由是什麼。簡單來說,「總之在進行研磨時,平坦化性能卓越」。我還記得當時的設備工程師老是誇張地說:「研磨就像毒品一樣。一旦用了就會上癮。」電鍍技術是在研磨技術之後才研發出來的,而工程師一樣是以誇張的口吻描述電鍍說:「一(研磨)不做二(電鍍)不休」。也多虧大膽的半導體工程師只要是能製造出性能好的裝置就會採用,我們才有今天的電鍍與研磨技術。

### 由大學與學會支撐的電鍍與研磨

古老的電鍍與研磨技術,因為上一節所描述的理由,而被應用到最先進的半導體產業上。但是既然技術古老,也就表示這個領域已經相當成熟。就連前面提到的 3K 技術,其實也是由有傳統的大學與企業支持的。基於以上歷史背景,現在就來介紹電鍍與研磨技術如何演變為高科技技術。

# 來自克拉克森的問候

•••••

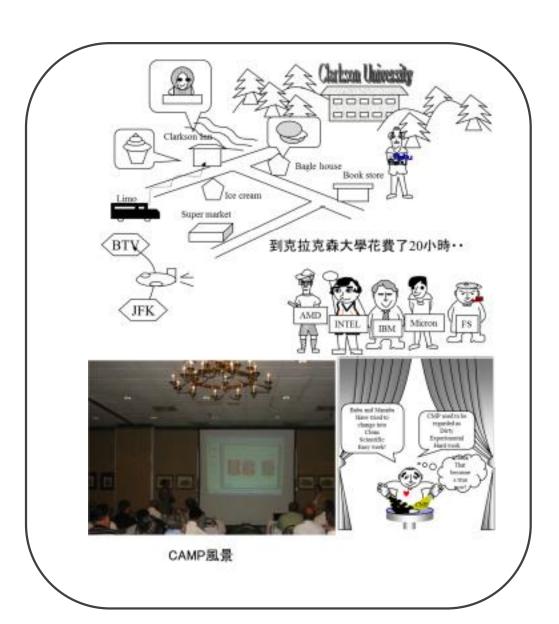

### 來自克拉克森大學

要到波茨坦 (Potsdam), 得先從成田機場坐 12 小時的飛機, 到美國紐約的 JFK 國際機場, 然後再轉搭歷時 90 分鐘的美國國內線飛機到伯靈頓機場, 最後再搭 4 小時豪華轎車。波茨坦是克拉克森大學的所在地, 人口為 13,000 人, 幾乎所有居民都跟大學有關係, 也就是所謂的大學城。

我自從 2002 年受聘為克拉克森大學客座教授以來,每年夏天會訪問該大學—個禮拜講課 (或作研究 開學會)。為什麼每年跑到這個僻里(失禮了)? 那是因為克拉克森大學是研磨(CMP) 研究的中心。

克拉克森大學是具有百年歷史的大學,在奈米粒子領域早就有實際成就,並且應用奈米粒子展開研磨技術研究。前副校長、目前擔任特別教授的 S.V.Babu 教授專注於 CMP 研究,目前教授的學生們,已經散落在 Intel、IBM、Micron 等大廠,可說是一手拉把 CMP 技術長大的人。從「只要在CMP相關會議的會場裡丟一顆石頭,肯定會打到克拉克森大學校友」的玩笑話就可窺知,克拉克森大學在此領域的重要性。

### Lake Placid CAMP 的報告

克拉克森大學每年都有舉辦 CMP 的國際會議 在 2007 年, 也就是今年, 第 12 次 CAMP 會議在美國 Lake Placid 舉辦。在這個會議裡 來自世界各地的 CMP 工程師 科學家齊聚一堂, 在為期三天的會議中, 討論半導體裝置平坦化技術的最先進話題。

本書整理了克拉克森大學客座教學及在 CAMP 中發表的內容, 廣泛包含適合學生到從事最 先進研究的裝置工程師之內容, 有些甚至涵蓋在 CAMP 舉辦的Dinner Talk (適合家庭閱讀)等, 內容可謂廣泛過頭, 但仍希望讀者能享受各類主題。 (筆者的藉口)

關於克拉克森大學與 CAMP , 稍微摻雜了我的個人經驗, 在進入本題之前, 我想先介紹兩個故事。這些故事包含著電鍍與研磨及半導體業界的精髓, 希望讀者能詳細閱讀。技術細節就在讀完故事後再試著理解吧。來自克拉克森的問候

# Planarization Carol平坦化頌歌

狄更斯著作的《小氣財神(A Christmas Carol)》是我很愛看的書,所以如果前文「平坦化頌歌(Planarization Carol)」内容與其有雷同之處,也請多多包涵。

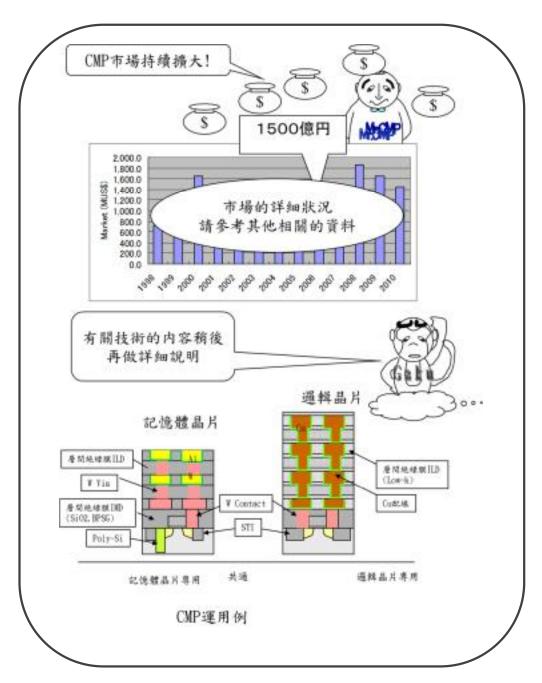

# CMP 前景光明!?

前面已經提到,沒有任何一句諺語比「溫故知新」更能闡述開發的基本。早在西元前700年就已經開始運用的鍍膜技術,以及用於磨製石器的研磨技術,兩者結合之下,到了21世紀,居然為半導體製造技術掀起一股鑲嵌製程的革命風潮。研磨技術是在1980年代初期,由IBM 所研發出來的層間絕緣膜平坦化技術。只是當時IBM 捨棄了單純的"研磨" (Polisher)字眼,改用"CMP"一詞(Chemical Mechanical Polisher)。您是否有發現到,其實這個專有名詞,對於開發有著重要的意義呢?如果只是單純地講研磨,就脫離不了古老的印象。但是換成 CMP 後,就很神奇地會覺得,好像可以應用於開發新型半導體似的。從 CMP 的故事可以得知,重新檢視前人的知識,以其為根基加以創新,這就是溫故知新與開發的範本。

2006年,CMP的產值約為14億美元(約1600億日圓)。日後CMP應用範圍應會持續擴大,同時使產值持續上升。負責開發CMP的人似乎會笑到合不攏嘴?順帶一提的是最新的CMP應用,可區分為邏輯與記憶體兩方面,其應用範圍從層間絕緣膜一直到鎢接點(Tungsten contact)、Via、STI(Shallow Trench Isolation)、Cu配線等。

但是,這樣下去真的沒問題嗎? 半導體製造業的興衰歷史循環,會在何時來臨? 又會發生什麼事呢?

### 參加 MRS 學會

在此想向各位介紹我的一項體驗心得。2007年4月,我受邀參加 MRS 國際學會的 CMP 項目,因而前往舊金山。這項體驗就是在那次的學會中經歷到的。不知道您是否會相信以下的故事。

# 精靈出現

•••••

### 三位精靈

當時已經一段時間沒來 MRS 了。1998年與克拉克森大學的 Babu 教授共同擔任聯合主席時,曾有多次擔任客座演講的經驗,但是 MRS 的 CMP 部門,最近幾年都不曾舉辦活動。今年卻是連續舉辦三天,盛況空前。然而,我這幾年累積了不少疲勞感,就算是參加學會,仍然很快就會睡著。

有幾次還囂張地在內心想:「唉,又是學生發表論文啊...。」今天雖然也想好好聆聽演講,卻不知不覺地睡魔來襲...

### 年邁紳士的出現

突然間,四周變暗了?

好像在哪兒見過面的年邁紳士開始對我說話。

年邁紳士: 「Manabu 先生,我知道你現在似乎在 CMP 領域很有成就,但是從明天開始的三天期間,在晚上十一點,會有精靈們來找你。請你仔細聆聽他們說的話,不要懷疑,好好地思考他們說的事情。」

我内心一直在想,這位紳士好像在哪兒見過,但又因為時差帶來的疲勞而睡著了。 隔天...

(打個岔) 請讀者不要去思考, 感覺這樣的情節似曾相似。

不過我的確是狄更斯的書迷,或許是受到在飛機上閱讀的《小氣財神》影響。

### 第一位精靈(古代)

第一天晚上的十一點,精靈真的出現了。不過看起來好像是原始人。

「Mana~bu, 讓我帶你回到古代。|

粗魯的精靈才剛講完,就抓著我的頭把我拉回古代,一瞬間就到了西元前的世界。在那裡有西元前的先人們,正在用石頭磨著石頭。男性費力磨製石器,而女性則用石頭磨製珠子。

精靈: 「Mana~bu,研磨可是從神話時代的先人們開始,就費盡干苦萬苦流傳下來的技術啊。絕對不是你們自行發明的技術。要溫故知新,別忘記先人的技術啊!」

平坦化頌歌

# 現在、古代、未來

•••••

# 第二個精靈 (現代)

隔天又一位精靈現身了。這次是現代的精靈。

精靈:「Manabu 先生,你覺得昨天的古代精靈怎麼樣?我是現代精靈。我們來看看現在 CMP 是如何應用的吧。」才剛說完,四周就變得一片漆黑。

我:「這是哪裡? |

仔細一看,旁邊有細菌爬來爬去,還有人員穿著上面寫著有機物、金屬等字眼的髒衣服走來走去。

精靈:「這是正在研磨的『石頭(晶片)』內部。你們或許還在自滿,覺得 CMP 是已經完成的技術,但其實還有一堆像是腐蝕、裂痕、剝落、空洞等問題。現代的「講話石」正在喊著,快點來救我們吧!」

# 第三位精靈 (未來)

然後,到了最後一天,最後一位精靈出現了。他戴著黑斗篷,一語不發地站著。

我:「精靈先生,你今天要給我看什麼東西?第一天我回到傳說時代,遇見辛苦磨石頭的先人們。 昨天去看在先進半導體業界被虐待的講話石。那今天是要...?」

戴斗篷的精靈默默地指了指在 CMP 國際學會中汗流浹背說明最新技術的年輕工程師與科學家。

精靈: 「Manabu 先生,因為先人與當時研究研磨的人們非常努力,才會有今天的 CMP 榮景。在日本,也有平坦化 CMP 委員會自 1994 年以來持續努力著,將各種構思發揚光大。幸好 CMP 的用途,從層間絕緣膜開始,一直延伸至鎢、Poly - Si、STI、Cu 鑲嵌等,最後還應用在金屬鑲嵌閘門等新材料的研磨上,其成長之勢銳不可擋。但是,沒有科學就沒有發展。請務必、務必告訴從事 CMP 的各位,不要對於現在的盛況感到自滿,請更加努力鑽研。」才剛說完,他就脫下斗篷。原來他就是第一天出現的那位年邁紳士。

我:「啊,你是...」

沒錯。他就是在 CMP 業界裡,無人不知無人不曉的 Babu 博士。

# CMP化為永恆

•••••

### 與Babu共同研究

聽到 Babu 這麼說, 我這才覺醒過來。

仔細想想, 半導體就是一連串的盛衰循環。

CMP 也不可能一直維持現狀。

事實上,世上的各種科學思維不斷地大幅改變著。註)

而 CMP 與鍍膜也是脫穎自從古代思維的技術。在它們的背後存在過默然消失的技術。 那麼鍍膜與 CMP 也...

(註) Paradigm shift 45 是筆者於 2005 年提出的警訊,內容為:「針對 45μm 之後的微型化、薄膜化與 45cm 大口徑化,以往的思維將產生巨大的變化。」容後詳述。

### CMP 化為永恆

這就是我參加會議時做的夢。無論這個夢有什麼含意,現在 CMP 的確銳不可擋。然而正如前述,以往的革命技術都只是歷史盛衰的一部分,我們這些從事 CMP 領域的人員不能自滿於當今榮景,而應該更努力發展 CMP 才對。以前 CMP 的 P 代表 Polisher。但在 1998 年的 MRS 之後,我與 Babu 教授商量後,將 CMP 的 P 改為 Planarization,因為平坦化技術並非僅局限於研磨。

平坦化還有許多問題得解決,而那些問題得靠 CAMP 學會等年輕工程師的技術來解決。這次 我真的覺醒了,我發誓我再也不可自滿,要繼續精進相關知識與技術,讓 CMP 在將來的十年後、 二十年後仍保有一片榮景。

### CMP 永不消失!

以上是鍍膜及 CMP 歷史與現況的第一篇故事,學生是很喜歡,不知讀者各位有何心得?

接下來將介紹能夠綜觀半導體業界的第二個故事。

# Paradigm正在變化中!

Bell Best Project "X"計畫?

# "X" 計畫?

以下我要介紹的故事,是由假想的商品開發公司、晶片廠商、設備廠商進行機器人開發計畫,並且在故事中加入商品、晶片、設備與半導體產業的主題,讓各位在這一章中先對整體有初步的概念。至於各項技術的詳細內容,則留到下一章說明。

# Bell Project 開始!

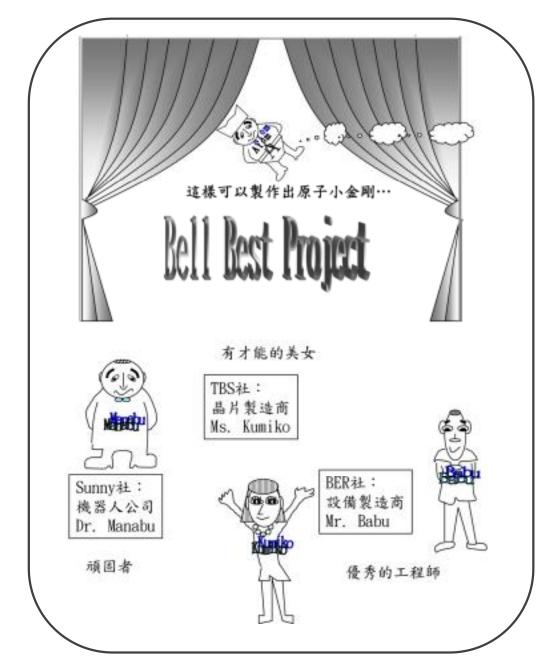

首先介紹本故事中的登場人物。

- ·機器人公司 Sunny 的 CEO Dr. Manabu (非常頑固而且任性)

- ·晶片廠商 TBS 的部長 Ms. Kumiko (非常有能力的美女)

- · 設備廠商 BER 的部長 Mr. Babu (聰明的工程師)

故事是從某天下午 Sunny 的辦公室開始展開。

Sunny CEO Dr. Manabu 想製造和原子小金剛一樣的機器人,於是開始執行機器人的開發計畫。究竟會發生什麼事呢?

### 各場景如下:

- · 場景 1 想製造機器人 (I want Atom!)

- ・ 場景 2 食物鏈 (Food Chain)

- · 場景 3 Bell Best 計畫 (Bell Best project)

- · 場景 4 Concept first

- · 場景 5 產品藍圖 (Roadmap)

- · 場景 6 Bell 晶片廠商開發 (電鍍與研磨)

- · 場景 7 下單購買生產設備 (Order!)

- · 場景 8 機器人因此誕生 (Bell Boy!)

希望讀者們能不厭其煩地讀到最後。故事即將開始。

# 原子小金剛終於誕生?

••••••

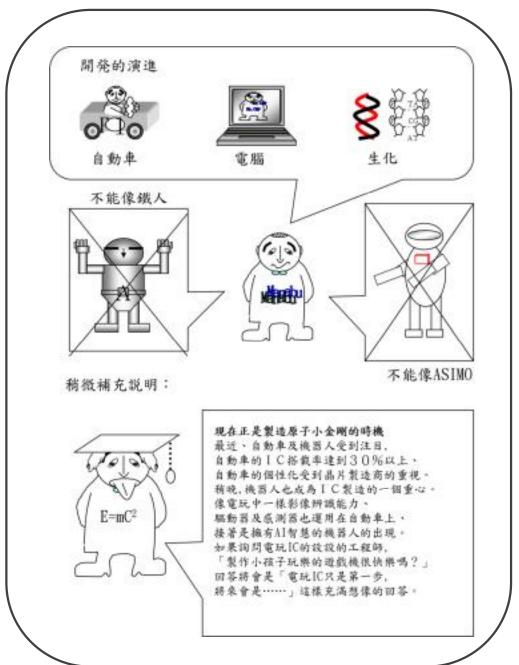

# 場景 1 想製造機器人 (I want Atom!)

這裡是 Sunny 的 CEO 室。Sunny 的 CEO Manabu 總是思考著未來。今日是讀書日,CEO Manabu 正在讀原子小金剛的書。

Manabu:

「技術革新從過去的汽車轉到半導體, 然後到今日的生化科技。接下來會是什麼呢?

對了! 是機器人! 但是我不要 Asimo 或鐵人那種吱吱嘎嘎的機器人,我想打造像原子小金剛那種非常接近人類的機器人。這個開發計畫一定需要半導體晶片廠商的協助。好! 就開始製造像我一樣聰明的未來機器人的計劃吧! 」 接下來好像會往意想不到的方向發展...

在這裡先補充說明一下後半導體 。

### 何謂後半導體?

半導體業界從過去效法成熟產業的技術來進行發展。現在輪到半導體產業將技術借給新興產業。那舞台在哪?

沒錯,MEMS、奈米技術與生化領域是前幾名候補。日本對科學技術的努力程度,可以從經濟產業省發表的預算得知。能源與環境是日本國家政策的重點,但最近幾年 IT(資訊)/BT(生化)/NT(奈米技術)等領域的預算也得到大幅提升。也就是說,Long Term R&D 應該致力將 IT(資訊)、半導體領域所培育的技術應用到 BT(生化)與 NT(奈米技術)領域。

那半導體領域培育出來的技術有哪些?有微加工技術、奈米加工技術、生產設備技術、處理技術等等,如何將這些技術應用到新領域上是很重要的。從短期來看,這些技術會應用在數位家電上,中期將應用在車載設備上,長期則是應用在生化、奈米技術以及機器人上。這些應用領域與半導體的未來將日漸光明,半導體是絕不會消失的!

# 弱肉強食食物鏈

.....

# 場景 2 食物鏈 (Food Chain)

讓我們回到故事場景。 Manabu 立刻叫秘書進來。

Manabu:

「晶片的開發找 TBS 吧。馬上打電話給 Ms. Kumiko,她一定會幫我們製造出很棒的 SoC (System On Chip)。

還有製程生產設備就找 BER,馬上聯絡 Mr. Babu,不管什麼要求他一定都能立刻做到。」 老闆一聲令下,秘書忙得手忙腳亂,突然得從 Food chain 的上游聯繫到下游。

(註) Sunny 並非 SONY,TBS 也並非東芝,BER 更非荏原,請讀者不要錯誤解讀。

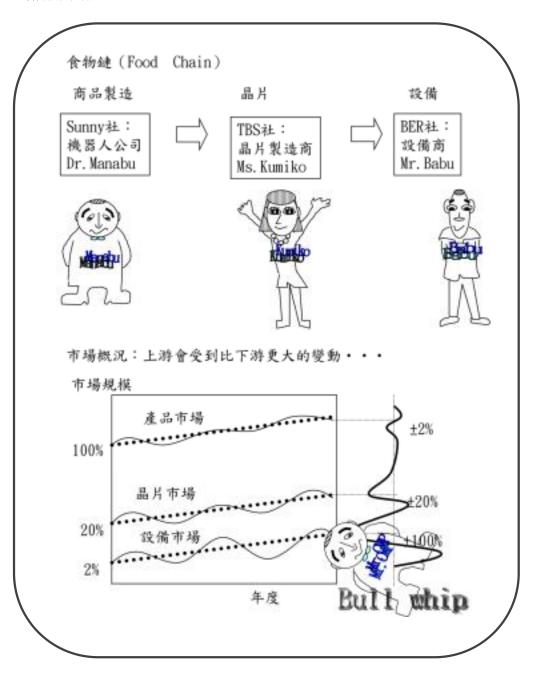

半導體 Food chain (Supply Chain) 是由商品開發廠商 > 晶片廠商 > 生產設備、材料廠商 所構成。以前我曾在 ITPC 半導體晶片廠商 VIP 集會中,開玩笑地說這是弱肉強食的食物鏈 (Food chain)。而我所創造的 Food chain 一詞,現在似乎也變得廣為人知。

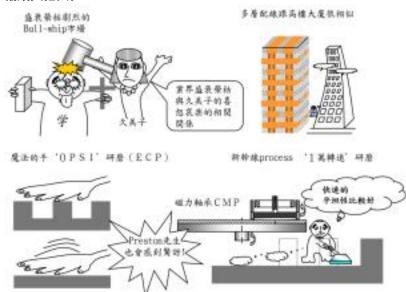

# 半導體業界市場規模

若將商品開發產業設定為 100%, 那麼晶片產業大約是 20% (可想成半導體在商品內所占的比例), 而生產設備則不超過 2% (相當於晶片產業的投資額的 10%)。雖然尚未達到「一人得道難犬升天」的地步, 但商品開發市場只要有 2%的變動, 晶片市場就會變動 20%, 生產設備產業也會隨著出現變動 100%的幅度, 因此也有人稱其為 Bull Whip (牛尾)產業。

總之,這是個極為辛苦的業界。

# ·機器人名稱是 Bell Boy!

# 推動專案

.....

# 場景 3 Bell Best 專案 (Bell Best Project)

Manabu 的一聲鶴唳(還是豬的咆嘯?)下,全員集合。我們來窺看一下會議室的景象吧。

Manabu: 專案名稱很重要。先從晶片命名開始吧。

叫「Cell」如何?

Kumiko: 等一下! 那是東芝和 SONY 的晶片吧!

Manabu: 對喔! 那叫「Bell」呢? Kumiko: 嗯~,聽起來很像...好吧。

Manabu: 再來就是專案的名稱! 隨便什麼都好, 快取個名稱吧!

Babu: 那就叫 Bell Best, 您覺得如何?

Manabu: OK OK OK...

於是 Bell Best Project 就這樣展開了。

實際上,專案命名大致就是如此。對帶頭者稍微的妥協,然後底下人一起推動專案。

究竟這項 Bell Best Project 做出來的機器人會如何...

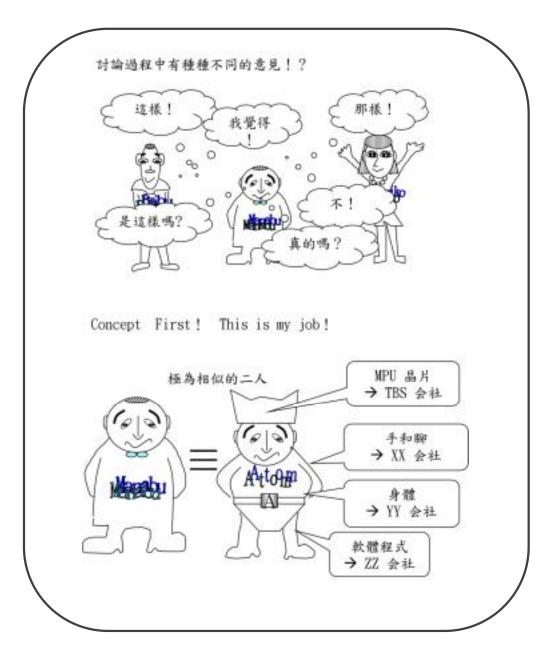

# 場景 4 Concept first

Manabu 怎麼樣都想製造出跟自己一模一樣、有如原子小金剛一般精巧的機器人。抛了一句「設計圖我來畫」後,就自顧自地開始著手最重要的產品工業設計。工業設計是展現初始設計概念的重要元素。雖然也有在完成產品設計後再進行工業設計的例子,但原本應該是由設計工程師先展開工業設計才對。

這樣的設計圖真的可行嗎?這該是首要關注的吧?而且Manabu就連下包商也一個接著一個全都自己決定了。真是任性的人啊。

頭腦由 TBS 負責、腳是 X X 公司負責、身體是 Y Y 公司負責、軟體則委託 Z Z 公司。最後,機器人的名字叫...

嗯,新開發處理器是叫做 Bell,那就叫 Bell Boy 吧! (真的好嗎?)

然後就交給專案團隊進行。整理一下發展到目前的狀況:

- ·新開發的處理器晶片名稱是 Bell

- ·所以計畫名稱是 Bell Best Project

推動專案

# 擬定產品藍圖

••••••

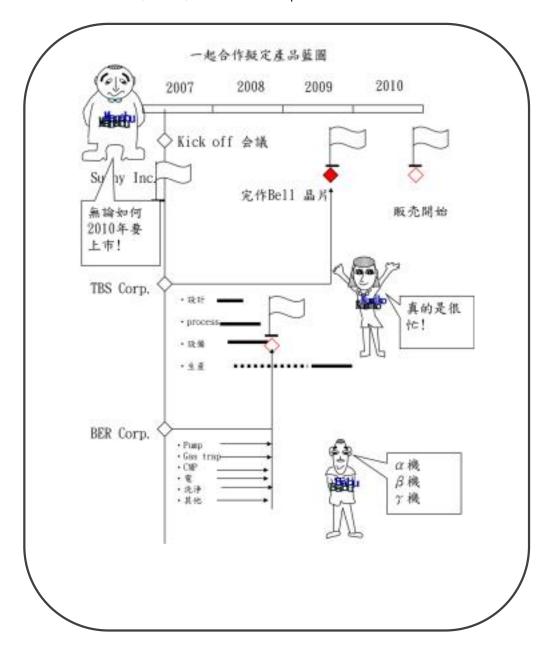

# 場景 5 產品藍圖 (Roadmap)

產品藍圖與單純的時程表不同,產品藍圖的重點在於設定專案中各成員各階段里程碑, 並且 腦盡腦汁朝該目標邁進。

### 商品開發公司的產品藍圖

本例子中 Sunny 擬定的產品藍圖相當重要。先進行市場調查,並將 Bell Boy 的開賣時間設定在 2010 年年底。正好是聖誕節旺季!也就是說 Bell 微處理器得在 2009 年年底完成才行。接著把這個結果轉達 TBS。

然後 Kick Off Meeting (專案開始會議) 就定在 2007 年 1 月的元旦! (這人真是任性啊)

### 晶片廠商的產品藍圖

從商品開發公司得知處理器的交期後,就可以研擬處理器開發的詳細時間表了。考量設計、 製程、製造的流程後,決定在 2008 年年底導入生產設備。決定需要哪些生產設備後,就把結果 告知 BER 吧。但或許還會想著,要是稍有差池來不及可就頭痛了,還是早點告知吧。

曝光設備 XX 之前交貨

CVD 設備 XX 之前交貨

RIE 設備 XX 之前交貨

CMP 設備は XX 之前交貨

電鍍設備は XX 之前交貨

洗淨設備は XX 之前交貨

排氣系統...等等。

### 設備廠商的產品藍圖

最後就是設備廠商的時間表了。總之就是配合晶片廠商指定的里程碑盡最大的努力。如果是 發展成熟的設備還好,但是開發生產設備可沒那麼簡單。首先要在公司内

擬定產品藍圖

部驗證 (α機), 再來是送到晶片廠商進行驗證 (β機), 最後才是交出量產機 (γ機)。

# 何謂TEG?

### 場景6 Bell晶片廠商開發 (電鍍與研磨)

先來聽聽 CMP 工程師 A 先生與 Babu 的對話。

Babu: 「A 先生,這次 demo 的結果不太好耶。使用者給的初始 profile 跟底層結構結果怎麼樣啊? |

A 先生:「嗯? 什麼初始 profile? 才不會去測那個啊。而且底層結構也是機密。」(自信滿滿地說)

反被將一軍的 Babu 反擊說:「但是…但是不知道初始誤差跟模式密度的話,你能保證研磨性能嗎?」

A 先生: [...]

再來聽聽同公司的電鍍工程師 B 先生與 Babu 的對話。

Babu: 「B 先生,這次 demo 的結果不太好耶。使用者的電鍍 TEG 構造很複雜嗎?模式特別嗎? |

B 先生: 「嗯? 什麼電鍍 TEG? 別家廠商怎麼可能告訴我模式。那是別家廠商的機密。」 (自信滿滿地說)

又被反將一軍的 Babu 反擊說:「但是…但是不知道密度模式的話,你能保證電鍍性能嗎? |

B 先生: [...]

Babu:「嗯~看來不好好教一教 TEG 可不行...」

以上情況在設備廠並不少見。來好好地學習一下晶片吧。

# TEG 晶片

來了解一下 TEG (Test Element Group) 吧。我們熟悉的電鍍與研磨用的 TEG 實際上用在晶片的哪部分?為什麼需要要求電鍍與研磨的性能?

詳細内容會在下一章介紹。

# 了解晶片

••••••

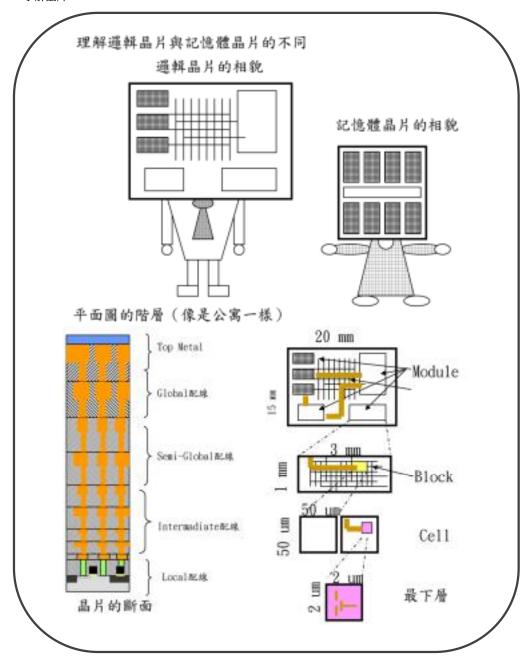

### 晶片的面貎

晶片主要分記憶體晶片與邏輯晶片。(詳細分類請參考專業書籍)

讀者應該知道記憶體晶片與邏輯晶片看起來完全不同。記憶體晶片是在晶片內記憶體能塞多少就塞多少; 邏輯晶片則是依使用者需求有很多變化。電鍍與研磨是應用在各階層處理這些面貌各異的晶圓。

# 何謂平面圖?

晶片設計是從名為平面圖 (Floor Plan) 的概略設計開始。

- ·首先設定整體設計。(在哪設置哪個模組)

- ·接下來規劃模組內的設計。(block 該在哪裡)

- · 然後 block 内設置 Cell。

### TEG

再來了解一下 TEG 吧。TEG 分以下四種階段。

階段 1: BEOL 開發用 Metal Open, Short Via-chain 等電氣特性

其他可選擇的 TEG 還有 CMP 用與電鍍用

階段 2: FEOL/BEOL 邏輯等驗證用

階段 3: FEOL/BEOL 附 TEG 晶圓,本體周邊有 TEG 區

階段 4 : 已將 TEG 切離的量產用晶圓

每間公司有其各自的作法,每種晶片在各階層的配線、尺寸、設計也都不同,只要明瞭開發電鍍與 CMP 處理單元上存在特別選項的 TEG, 就算沒有任何資訊也不需要做電鍍與研磨的 demo吧。

也可利用其他 TEG 專業廠商為某個目的而專門開發的 TEG 晶圓。

Bell Best Project Bell Boy 完成!

# Bell Boy 完成!

.....

# 場景7 下單購買生產設備 (Order!)

接下來終於是選擇 BER 的生產設備。從曝光、注入離子、成膜、蝕刻、CMP 、電鍍、排氣系統到廠務系統,最後總算是趕上排程。

這樣專案就會成功嗎?

哪這麼簡單。SoC 其實有些問題!

什麼問題請參看之後的章節 - 多層問題。總之問題很多。

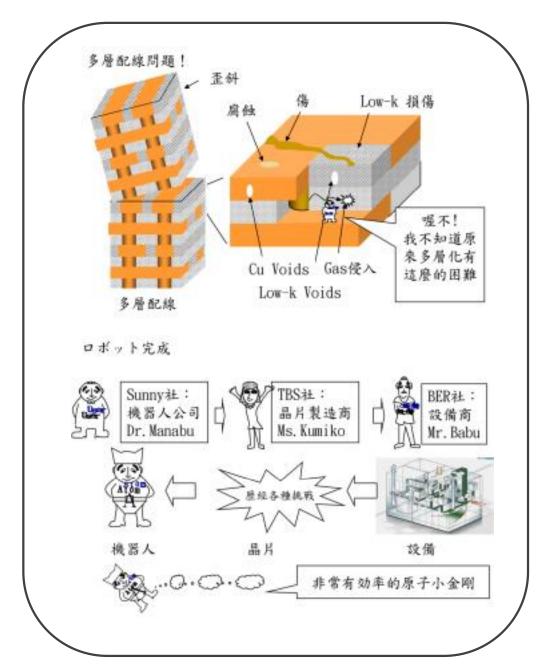

# 場景 8 機器人就此誕生 (Bell Boy!)

我嘗試性地用圖來表示多層配線問題。

詳細內容會在之後的章節描述,總之就是絕緣膜有一堆洞,銅配線也是有裂痕、腐蝕一堆問題,結果就是完全不具可靠性。面對如山一樣的問題,唯有仰賴開發才能解決。就讓我們跟著大學或學會,朝次世代晶片開發邁進吧。

34

幸好眾人之力完成的機器人 Bell Boy, 現在還在某知名飯店工作...吧?

故事到此結束,故事裡包含了許多基本概念。

望讀者能多讀幾次。我在大學運用角色扮演的方式講課時採用了這個故事,評價很好。

接下來正式進入技術問題。

# 第一次的 Dinner Talk

我在 2003 年第 8 次 CAMP 會議中,第一次規劃了 Dinner Talk。CAMP 每年約有100位工程師以及家眷參加。主辦單位除了希望讓家眷也融入其中,,也希望讓孩子們了解自己父母的工作內容。在經 Bob 教授的授命下,我擔任了第一次 Dinner Talk的主講者。

在演講中我介紹說半導體業界是由商品、晶片、設備(材料)形成的食物鏈。這個業界變化之快速,遠勝於久美子(家內)的喜怒哀樂的殘酷業界。還說明了最近的多層配線的難度有如建造高層大樓,需耗費極大努力才能完成。最後我還介紹了CMP的最新技術 "0 PSI 研磨!"與"一萬轉研磨!"等技術,這些革命性的技術足以令普雷斯頓教授也嚇到腿軟(?)。

Dinner Talk 結束,我滿身大汗地從講台上走下時,一位約十歲的可愛小女孩靠過來對我說「Good job!」。看來至少我的英文他們還聽得懂,這才令我稍微安心了點。在那之後我一直持續參與 Dinner Talk,今年是第十二屆,會場的笑聲指數從未輸給其他人。

# 第 II 篇 Wet Deposition Process:

Plating濕式薄膜沉積製程:電鍍

# 從水桶到半導體電鍍

### 從世界最古老的電鍍到最新技術的電鍍

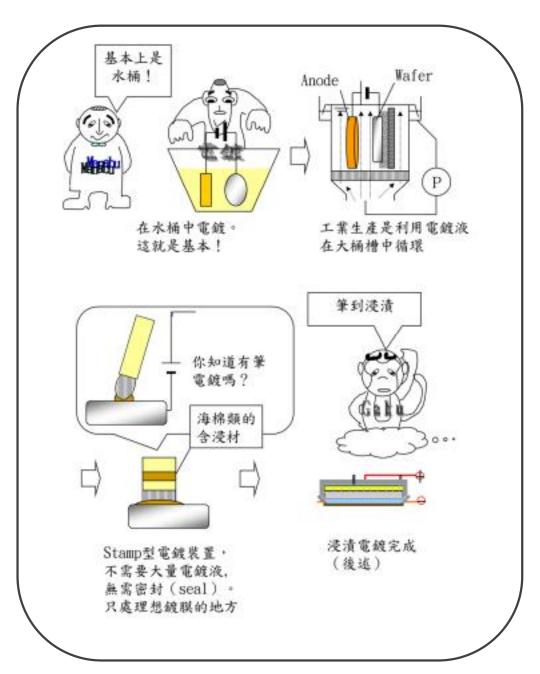

電鍍在西元前就已經出現,是世界上最古老的技術之一,在四世紀左右經由中國與朝鮮傳入日本。電鍍在日文中有時寫成「meki」或「鍍金」,這裡我們就統一稱作「電鍍」。我總是說:「電鍍開發的基礎,是在水桶中嘗試出來的。」為什麼呢?溫故知新。讀者只要了解電鍍的歷史,搞懂電鍍的原理,一定也會放棄打造高價的設備而跑去買水桶。

請看下一頁的圖。雖然這個之後還會再提到,不過對於電鍍,只要我們把銅板跟想要鍍膜的東西,放到類似水桶(例如)的大電鍍槽(bath)裡,再加壓數伏特的電壓就可以完成鍍銅。非常簡單對吧?電鍍的基礎不過就是如此。但是,如果要將這種作法運用到工業上,就得加上許多零件才行。實務上半導體用電鍍設備是讓電鍍液在大電鍍槽裡不停循環,並將陽極(電極)與晶圓(要電鍍薄膜的產品)分別設置在兩側所構成。

以這個構造為基礎而發展出的點子更是令人眼花撩亂。例如運用「電鍍筆」原理的Stamp型電鍍裝置,不需要大量電鍍液,也無需使用電鍍裝置中最難搞的密封(seal),就能只處理想鍍膜的地方。而更進一步發展這個技術所得到的就是「浸漬電鍍裝置(後述)」。

### 半導體應用電鍍技術歷史概要

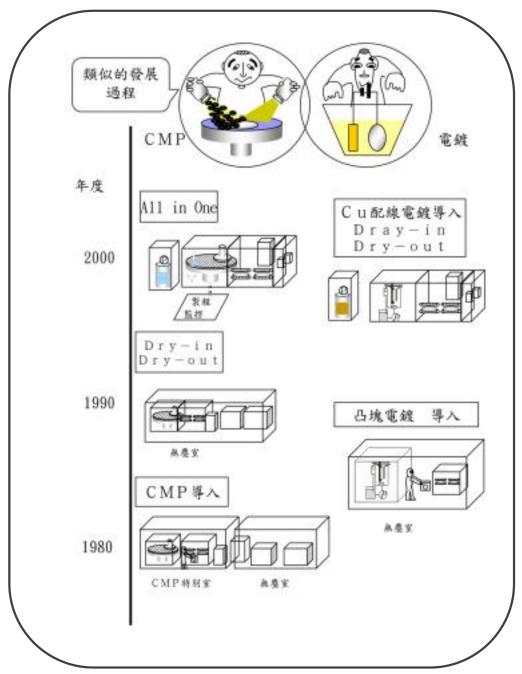

本節介紹半導體應用電鍍技術相關的歷史概要。無論是就發展時期還是技術性能上來說,半導體製造用電鍍技術都應該分為兩個時期來探討。第一期是開發並運用於八零年代後半的凸塊電鍍技術。這個製程是將金填入大約40µm見方×40µm高大小的孔內形成金凸塊(電極)的製程,是一種鍍膜量數十µm級的鍍膜技術。第二期是開發並運用於九零年代後半的配線電鍍技術。這個製程是將亞微米級的孔洞或溝槽按照設計排列整齊,接著將銅填入其中而形成配線的技術。41頁的圖可看出研磨與電鍍在開發與使用時期上的相似性。兩者都曾被稱為骯髒、困難與憑經驗的3K產業,也都經歷過從外建洗淨到內建洗淨,並加入螢幕監控等開發歷程。不過由於半導體產業先採用的是研磨技術,所以等到電鍍加入半導體製程時,採用電鍍的過程已經不像研磨這麼費工夫。

# 從舊3K到新3K

#

那麼我們先來談談第一個金凸塊形成製程裝置的特徵。

雖然半導體晶片用金凸塊會使用到鍍金技術,但考慮到電鍍製程會產生重汙染,因此這個製程的設備並非設置於無塵室內,而是採用off line (無塵室外) 做法特別處理。鍍金製程會在反應室周遭產生大量飛塵,除了會汙染晶圓以外,也會為電鍍裝置外部帶來汙染問題。雖然因為金凸塊製程屬於晶圓末段製程,對晶圓的汙染程度並不嚴重,但對外部造成的汙染卻很重大,因此不可能設在進行半導體晶片前工程的無塵室內。但是為了追求縮短交期,in line (無塵室內) 作業當然會比off line更具有絕對性的優勢。因此,在八零年代末期急需解決的問題就是如何把過去代表舊3K (骯髒、困難與憑經驗) 的電鍍技術改造成新3K (乾淨、簡單與科學) 的電鍍技術。半導體晶片製造用電鍍製程設備就這樣進入研發時期。

在這個時期,研發的第一目的就是研發出可以設置在無塵室內的乾淨設計,並提 高電鍍製程能力以滿足縮小凸塊設計間距的要求。

# 發展配線用電鍍設備

接下來的配線用電鍍製程,即是半導體晶片製造中的主要製程。1997年底,IBM 宣布將在邏輯晶片中採用銅配線,並使用電鍍製程製作。這是繼CMP發表後,IBM再度為業界帶來震撼。過去當筆者從事CMP開發時,目標是鑽研「不容一絲雜物」的超高真空技術,所以怎麼也沒想到研磨會被應用到半導體晶片製造上。如前所述,儘管電鍍技術已經於八零年代末期應用在晶圓凸塊電鍍設備上,但我依然沒想到電鍍也會被應用在配線製程上。我只想著以凸塊製程技術為中心發展周邊技術,以備未來電鍍配線的時代來臨。因為銅配線製程設備對汙染對策與細微化的要求,比凸塊製程裝置還要來得更高。

半導體製程中電鍍扮演的角色?

# 各種電鍍設備

接下來就讓我們來看看各種設備的歷史吧。電鍍設備的演變如圖所示。

# 縱型浸漬式

1980年代,在LCD驅動IC的金凸塊電鍍設備中,有一種稱為縱型浸漬式的裝置。 這是以蠟保護晶圓內面,然後浸漬在電鍍槽中的方法。由於這種方法在電鍍後的除蠟 作業很費工夫,因此便由Cup噴射式取而代之。

# Cup/噴流式

此作法是將晶圓朝下放置,由下往上噴射電鍍液的方法。由於這種作法不會上電 鍍液流到晶圓內面,因此可以防止薄膜在晶圓內面形成。但是這個方法仍有缺點與問 題尚待解決。使用這個方法會使金屬附著於晶圓端面,導致這些黃金在後工程切割晶 片時成為廢棄物。另一個缺點是,電鍍液中的泡泡會留在晶圓上,導致電鍍不完全。

# 新縱型浸漬式

為了解決上述缺點,業界因此開發出以特殊治具蓋住晶圓的內面與端面,並沿用 縱型電鍍作法形成新縱型浸漬式。

# 新Cup噴射式

這個作法以一邊旋轉晶圓一邊電鍍來解決上述Cup噴射式會起泡的問題。透過這個作法,電鍍液泡沫吸附晶圓表面的情況因此得以減少。

就這樣,堪稱世界上最古老的電鍍技術就此成為最先進的半導體製造技術。

42

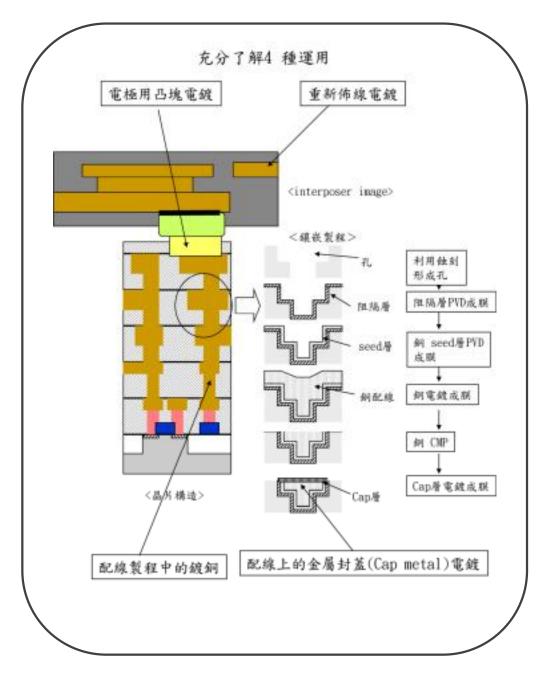

# 四個應用

半導體晶片用電鍍技術大致上分為以下4種應用。詳細內容將在後面描述。

# 電極用凸塊電鍍(黃金等)

半導體晶片多層配線的最後,連接外部(例如内插器)的電極稱為凸塊,以黃金等金屬電鍍加工製成。這些凸塊的大小與數量因晶片種類而異,但業界在1980年代就已經預測到未來凸塊會進化到大小只有十幾µm、數量達數千個,因此盡早開發並採用了適用於細微化的電鍍技術。

# 配線製程中的鍍銅 (Cu)

先以電鍍成膜,再透過研磨加工而成的銅配線製程,就是研發於1980年代,所謂的鑲嵌製程 (damascene process)。鑲嵌製程的作法,是先蝕刻絕緣膜形成配線溝,以濺射 (Sputter) 製程製造隔離層與薄膜層之後,以電鍍為銅配線鍍膜,最後再以CMP研磨配線。

# 配線的高熔點金屬封蓋 (Cap metal) 電鍍 (Co-W等)

銅配線被應用到多層配線後,電鍍技術也開始運用到半導體製造技術的其他各種領域。其中一例,就是銅配線電鍍後,在上面加工封蓋(Cap)的鍍膜技術。也就是所謂的高熔點金屬封蓋(Cap metal)技術,目的在於提高配線的穩定度。而技術詳細內容將於後描述。

# 重新佈線電鍍 (Cu或Ni等)

最後,當晶片配線要與外部連接時,需要變更配線的位置,而這個重新佈線的製 程當然也採用了電鍍技術。使用銅與鎳進行電鍍。

除了以上介紹的四個應用以外,電鍍技術,也就是濕式薄膜沉積製程的應用範圍,日後也必定會持續擴展。

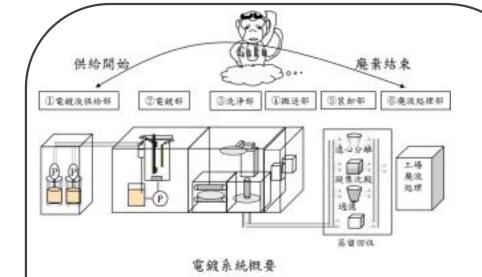

### 六個子系統

下圖為裝置概念圖。可看出與其他乾式裝置的概念圖完全一樣。

# 六個子系統

電鍍的子系統指的是: ①電鍍液的供給與管理、②電鍍處理、③洗淨、④搬運、⑤裝卸、⑥廢液處理。濕式薄膜沉積製程系統與CMP系統相似。

# 電鍍液的供給與管理

每家公司的電鍍液都不太一樣,但除了電鍍濃度管理之外,也都還包含添加劑、溫度、壓力、過濾等各種必備的管理。電鍍液供給裝置並非只是單純供應電鍍液,也執行著各種必備的管理。

### 電鍍處理

電鍍處理方法有很多種,這正是可以看出各家公司技術程度的地方。詳細將於後描述。

# 洗淨

洗淨與乾燥的規格視電鍍處理不同而異。但濕式處理的dry in與dry out是必要技術。而電鍍 後的表面改質也是洗淨製程的目的。

### 搬運、裝卸

搬運的過程可達成濕式處理平台共通化。實際上,我服務的公司所開發的電鍍裝置即採用與 CMP裝置完全相同的搬運與裝卸裝置。

### 廢液處理

在電鍍處理中,廢液處理是必備的步驟。特別是電鍍液的回收與再利用等環保設計,日後想必會愈加不可或缺。

# dry in與dry out

dry in與dry out曾是電鍍裝置普及的關鍵技術。特別是在300mm用裝置中被開發為微環境 (mini-environment) 。

### 整合

整合以上技術,建構出從電鍍液供給、鍍膜到洗淨及廢液處理的一貫化系統乃是需求所在。

電鏡装置外觀写真

# 從法拉第定律開始吧

談到電鍍,就得先從法拉第定律 (Faraday's Law) 說起。這是基礎中的基礎, 所以就擺在最前面說明。這與研磨的普雷斯頓定律 (Preston's Law) 同樣重要,要 好好記在腦海中。

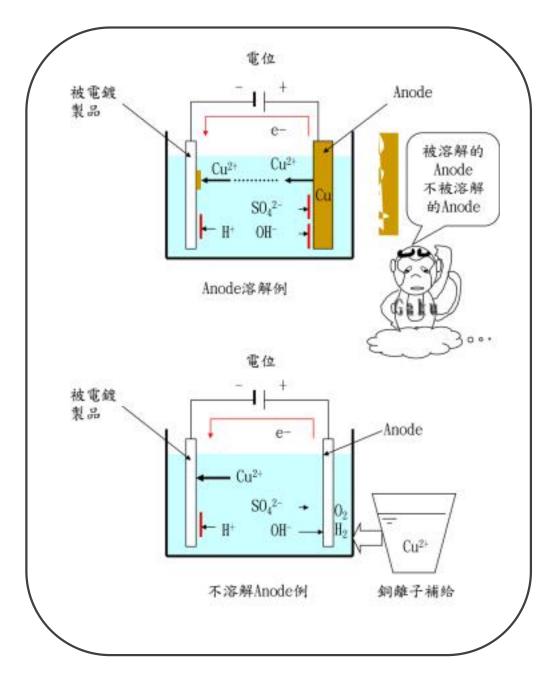

# 溶解陽極、不溶解陽極與反應式

陽極種類可分為溶解陽極與不溶解陽極。關於他們之間的差異,希望讀者能自行參考相關專業書籍。這裡以硫酸銅電鍍為例,介紹半導體電鍍技術中,至少一定要知道的知識。

溶解陽極的反應依以下反應式進行。施加的電壓為低於水電解反應的電壓 (I.25V):

水溶液中的離子解離 CuSO<sub>4</sub> → Cu<sup>2+</sup>+SO<sub>4</sub><sup>2-</sup>

陽極(十)反應

$Cu \rightarrow Cu^{2+} + 2e^{-}$

陰極 (一) 反應

$Cu^{2+}+2e^{-}\rightarrow Cu$

同樣的,不溶解陽極的反應則依以下反應式進行。

水溶液中的離子解離 CuSO<sub>4</sub> → Cu<sup>2+</sup>+SO<sub>4</sub><sup>2-</sup>

陽極(+)反應

$20H^{-} \rightarrow O_2 + H_2 + 2e^{-}$

陰極 (一) 反應

$Cu^{2+}+2e^{-} \rightarrow Cu$

# 法拉第定律的應用

讓我們來計算半導體晶片鍍膜時的銅的厚度吧。根據法拉第定律,銅鍍膜量與流動的庫倫量成正比。因以可從下述的算式輕鬆算出晶圓上Cu的鍍膜速度與鍍膜量。這很好用,要記起來唷。我們先用一般電鍍使用的電流密度(20mA/cm²)來計算。

# 根據法拉第定律:

電鍍析出量= (電流値) × (電鍍時間) × (Cu 1g等量)

可計算出電鍍膜厚為0.44µm/min (20mA/cm<sup>2</sup>)。

半導體製程中電鍍扮演的角色?

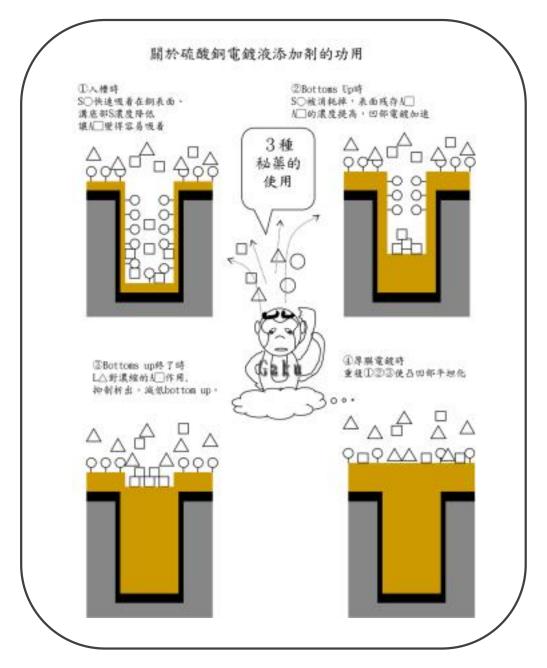

# 三個密藥

接下來針對添加劑的功用簡單描述。電鍍處理的技術就在這個添加劑裡,甚至可以說添加劑決定了所有的性能。添加劑基本上有: ①Suppressor (抑制劑)、②Accelerator (促進劑)與③Leveler (平滑劑)。以下針對各項功用簡單說明。

# Suppressor (抑制劑) (S)

此添加劑藉由氯附著在銅表面,抑制銅表面的電鍍析出,局部減緩析出並提升成 核密度。由於吸附初期時的平坦部及溝底部的吸附量不同,平坦部的吸附量較溝底部 的吸附量少,進而對Bottom-up產生影響。這種添加劑多以介面活性劑來擔任。

# Accelerator (加速劑) (A)

此添加劑會與Suppressor爭著吸附表面,具有降低電鍍析出電位的功能。此加速劑留在電鍍表面後,會因電鍍面形狀的變化使濃度局部上升,更進一步達到電鍍加速的效果。也就是說它會加速凹陷處的電鍍速度。有機硫磺化合物就是其代表例子。

# Leveler (平整劑) (L)

此添加劑具有抑制電鍍析出的功能。由於吸附效果會受到液體攪拌的影響,因此 滿底等液體流動緩慢、擴散層較厚的地方較難吸附。具有抑制Accelerator加速析出的 效果,提升膜厚平坦度的功用。季銨化合物等即是代表例。

上述只是非常簡要的說明,關於詳細內容希望讀者能自行參考電鍍的相關專業書籍。這3種添加劑有時也會只作為2種來使用。

# 半導體製程所要求的電鍍性能

.....

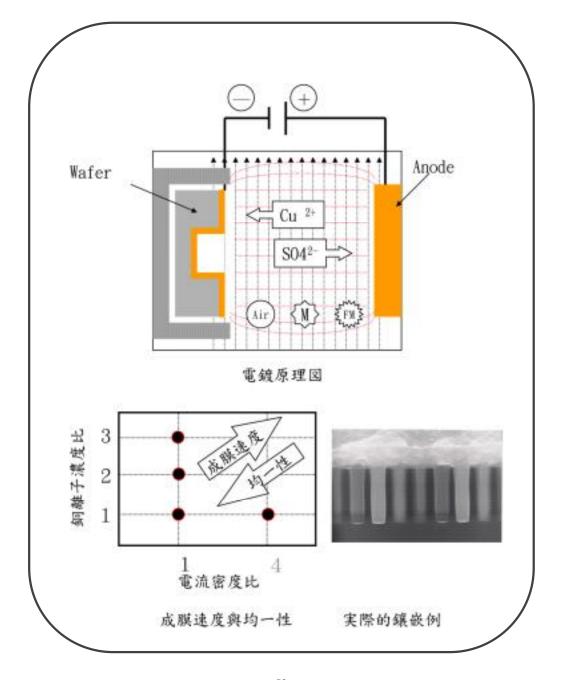

# 電鍍性能

電鍍性能是依據:①鍍膜速度、②鍍膜均一性、③缺陷 (defect)、④嵌入性、⑤膜的密著性、⑥電阻値、②膜中不純物等指標進行評估。

- (1) 根據法拉第定律, 鍍膜速度為電流密度與電鍍液中的金屬離子濃度的函數。

- (2) 鍍膜均一性是指將晶圓整體電流密度維持一定密度。因此需要維持晶圓 表面的電流或控制電場。

- (3) 缺陷是以Void(孔)、雜物、腐蝕、壞蝕的總數來評估。

- (4) 嵌入性會由添加劑來進行調整 隨著微細化的進展 嵌入也越來越困難, 有進行改善之必要。

- (5) 鍍膜與阻隔膜 (barrier layer) 的密著性同時也是關係到Electro Migration (EM) 的性能的重要評估項目。當然如果會發生剝落等情況 就連談都不用談了。

- (6) 由於在銅配線的情況下,低電阻化為主要的目的,因此目標大約是當塊體 (Bulk) 為  $1.6~\mu\Omega$  · cm時,配線約為  $2.2~\mu\Omega$  · cm。

- (7) 純度:照理來說首先應該徹底排除不純物才對,但是受控制的不純物能 提升EM耐性,因此又是必須的。

# 實例介紹

我用一般的硫酸銅電鍍,以電流密度與銅離子濃度作為參數的嵌入實驗為例。一般來說提升電流密度或Cu離子濃度,就能提高鍍膜速度,但此舉也會導致鍍膜的均一性變差。因此決定電鍍條件時必須同時考慮均一性才行。

# 流動視覺化

以上述内容為基礎的液流均一性,目前正處於應用電腦分析與流動視覺化技術研發Hydro Passage設計的階段。

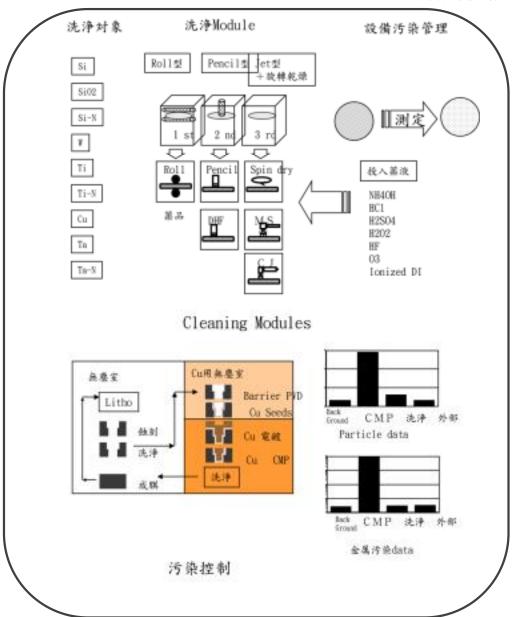

# 洗淨與汙染控制

# 洗淨

洗淨面是半導體製程上的各種材料(Si、SiO<sub>2</sub>、Si-N、Cu、Ta、Ta-N等),而要清洗的物質則是電鍍液及FM(Foreign Material)。在這麼多材料混在一起的情況下,若還要考慮避免腐蝕洗淨母材,就必須詳細瞭解晶片的製程。

洗淨模組的特徵如下所述。

- ① Roll型:以數百轉的轉速轉動Roll部材,同時清洗晶圓表面與内面,為標準裝置。

- ② Pencil型:以數百轉的轉速轉動Pencil部材,清洗晶圓表面,與①同為最廣為採用的標準。

- ③ Jet型: 此為一般噴射型再加上超音波功能的類型。可運用空蝕進行特殊噴射洗淨。 空蝕噴射可達到比過去噴射洗淨更廣範圍且更高效率的洗淨效果。其優異效果不 僅展現在平面晶圓上,若晶圓形狀有凹有凸,洗淨效果的差異更是倍增。

- ④ 旋轉乾燥:設置於②Pencil型、③Jet型模組上,進行最後乾燥的步驟。

# 汙染控制

Cu曾為半導體晶片的禁忌,當時要把Cu電鍍與CMP裝置擺進無塵室時可是掀起了一陣熱烈的議論。Cu相關的裝置在無塵室的Cu汙染控制設計有著很大的影響。在過去的錯誤嘗試裡,曾試著將Cu相關的裝置都擺到另設的空間,雖然安全但成本卻也很高。如果把Cu相關裝置擺在一般的無塵室內,雖然成本降低,但危險度又會增高。當然也可以兩相權宜,但這就得看各晶片製造商的工程師的選擇了。不管怎麼樣,就裝置上來說,氣流的設計得確實,避免對外部造成汙染。附帶一提,裝置的氣流設計已在CMP獲得驗證。

實際應用例

# 在微細尺度下嵌入pinch off孔?

<del>-</del>

# 對配線電鍍的要求

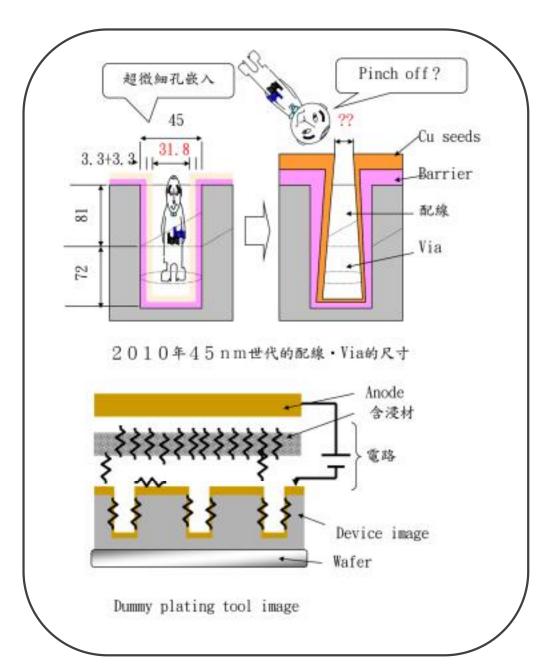

要想像未來對配線技術會有什麼需求,首先我們要先看ITRS2005年度版對2010年的要求值。電鍍技術要求的嵌入寬深比是配線部/穿孔部(1.8/1.6)。再加上阻隔膜厚3.3nm與薄膜厚3.3nm,實際寬深比為配線部/穿孔部(2.55/2.26)。還有阻隔膜前的酸化膜蝕刻側壁的粗糙面,再考慮到濺射的形狀,可以想像到嵌入形狀應該好不到哪裡去。除此之外,薄膜3.3nm的電阻值非常高,方圓300mm範圍內的不均也會變大。如果把此薄膜去除,阻隔膜就會變成電極,導致電阻值變得更高,原本方圓300mm的不均範圍會變得更大。結果,在微細趨勢的2010年45nm世代裡,要求的就是使用高電阻薄膜(含阻隔膜)來達到難以想像的嵌入形狀。

# 採用浸漬材料假電阻的電鍍方法

我再來介紹改善這個問題的革命技術吧。在以往的電鍍方法中,若薄化薄膜層厚度,晶圓半徑方向的面內均一性也會隨之變差。但如果在此方法中加入具有假電阻功能的浸漬材料,則既可薄化通電薄膜層厚度 晶圓半徑方向的面內均一性也不會變差,達大目前全球最高等級的電鍍性能(膜厚3σ、晶圓面內均一性10%;配線寬0.1μm、嵌入寬深比4.5的接觸孔)。

注)以前的(不使用具有假電阻功能的浸漬材料)循環電鍍方法中,當薄膜層厚度約為目前的60nm時,雖然也可以達到上述標準(膜厚3α 晶圓面內均一性10%;配線寬0.2μm、嵌入寬深比4.5),但卻達不到薄膜層厚度約20nm的標準。

在微細尺度下嵌入pinch off孔?

# 只有60cc大的電鍍槽?

.....

# 裝置概要

以下解釋裝置的陽極頭構造與裝置模組構造。

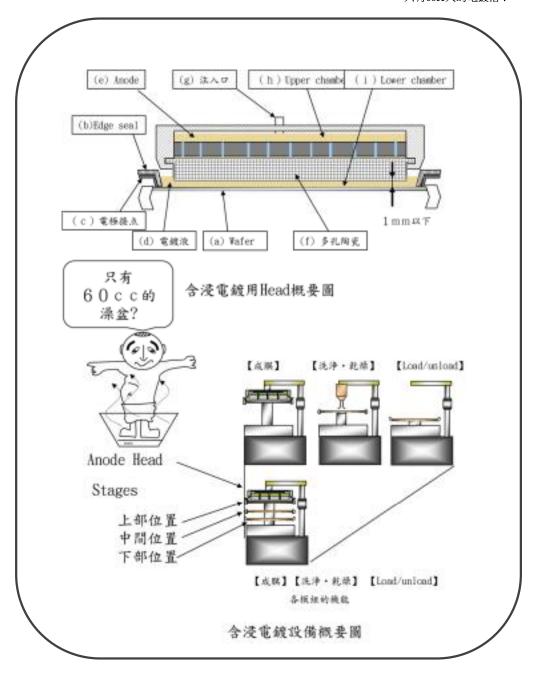

# (I) 陽極頭構造

晶圓朝上設置,並採用邊封 (edge seal) 內設有電極接點的 (dry contact型) 構造。電鍍液高度位於淹過晶圓1mm以下的狹窄間距內。陽極與晶圓之間配置多孔陶瓷作假電阻。電鍍液可從注入口供給上部與下部。

# (2) 裝置模組構造

裝置模組主要由陽極頭、處理平台(stage)及陽極待機部構成。運轉流程如下 所示。

- · 裝載晶圓至下部位置。

- · 移動至上部位置,進行前處理與鍍膜。

- · 在中間位置進行洗淨與乾燥。

- · 在下部位置卸載晶圓。

處理平台會隨著每個鍍膜製程上下移動,在下部位置運送晶圓進出;在中間位置進行前處理洗淨及乾燥;在上部位置進行電鍍。陽極待機部設有裝滿電鍍液的盤子,等待期間的陽極會保持浸漬在電鍍液中的狀態。陽極頭由含磷銅及浸漬材料(多孔陶瓷等)構成。藉由使用浸漬材料,可達到由黑膜保護陽極表面、防止陽極在移動中漏液及控制電場的功用。使用的電鍍液為硫酸銅,由於間距極窄,故只使用60cc。電鍍液會在電鍍前流入晶圓與陽極頭的縫隙之間,電鍍後再以吸嘴回收。

# 浸漬材料的氣孔率是關鍵

雖然前面提到用來作假電阻的浸漬材料為多孔陶瓷,但簡單來說就是類似輕石的東西。藉由限制液體的穿透率來提升表觀電阻。

實際應用例

# 有限元素分析法在這裡也用得上

.....

# 流動與電場分布分析

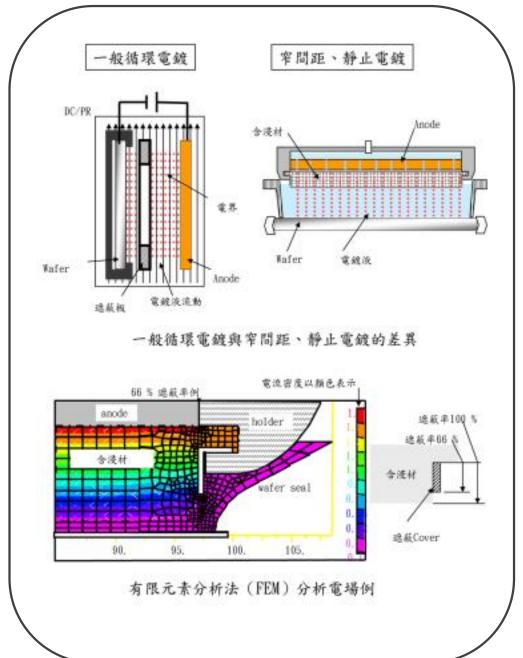

電鍍製膜速度主要是由電流密度與電鍍液的金屬離子濃度決定,因此鍍膜量的均一性可由電鍍液的流動與電場分布來控制。首先,關於流動與電場,我先來說明像浸渍電鍍那樣的窄間距,以及靜止電鍍與過去循環電鍍之間的差異。

|    | 一般循環電鍍 | 窄間距、靜止電鍍     |

|----|--------|--------------|

| 流動 | 控制為一致  | 因為是靜止, 故完全一致 |

| 電場 | 配合膜厚控制 | 配合膜厚控制       |

在以往的循環電鍍中,電鍍液在晶圓與陽極間循環,所以需要控制流動與電場。 而窄間距和靜止電鍍則因電鍍液是靜止的,電鍍液的流動範圍與晶圓的鍍膜表面完全 一致,因此,只要控制電場就可以控制鍍膜分布。

# 窄間距、靜止型電鍍的電場控制分析

以下為以有限元素分析法 (FEM) 分析窄間距、靜止型的電場之結果。

分析條件: Pre- and post-processor: FEMAP

Solver: ASTEAN

二維對稱模型

FEM的分析結果如圖所示。可看到晶圓附近的電位一致。

前面曾提到浸漬材料是輕石,這是因為氣孔率越少,假電阻的電阻就會越高,從 分析結果也可看到Terminal effect有減少的趨勢。但氣孔率少也就代表液體難以流動, 所以如何取捨以達到最佳化就是重點了。要研究這個問題,FEM可以幫上很多忙。

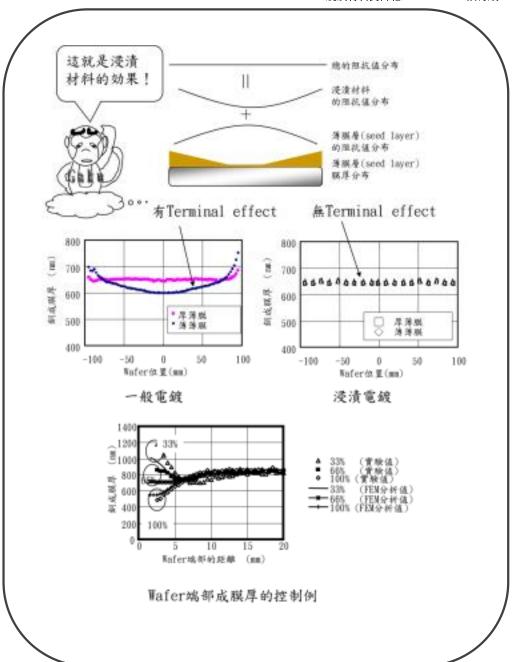

# 浸漬材料對降低Terminal effect很有效

# 通電薄膜層厚度的影響 (Terminal effect)

阻隔膜層(barrier layer)薄化後,薄膜層(seed layer)當然也會薄化。薄膜層的電阻與晶圓半徑方向距離有關,薄膜層薄化後,此半徑方向的變化會對鍍膜均一性造成影響。這個現象稱為Terminal effect,曾經是微細配線電鍍上的一個重大課題。採用一般電鍍方法並薄化薄膜時,越偏向中心,電鍍厚度就會越薄。但在採用假電阻(dummy resistance)的浸漬電鍍中,既使薄化薄膜,鍍膜仍可維持一致厚度。

# 也能控制膜厚

膜厚控制可透過改變假電阻氣孔率與遮蔽端部等方法來進行。如圖所示,透過改變假電阻材料的端部的厚薄度,可將其塑造為適合下個CMP製程的形狀。

# 採用假電阻的浸漬電鍍之效果

總的來說:

- (I) 若採用以往的(不使用具有假電阻功能的浸漬材料)循環電鍍時,當薄膜層厚度低於約20nm以下時,均一性會變差。

- (2) 使用具有假電阻功能的浸漬材料可薄化通電用薄膜層厚度。

- (3) 可藉由浸漬材料控制膜厚。

- (4) 晶圓面內均一性為3σ·3mmEE (Edge exclusion) 時,膜厚3%以下的目標已經達成。

使用具有假電阻功能的浸漬材料,窄間距與靜止電鍍概念的電鍍裝置已經能夠開發。以結果來說,這證實了世界最高水準的電鍍性能已經達成,也足以應對薄化通電用薄膜層(隔膜層薄化與薄膜層薄化)的需求。這代表著透過這個方法,對於32nm世代以後的薄化薄膜銅配線,也能透過電鍍來達成。

# 刺蝟製程

# 鍍膜平坦化

過去鍍膜的歷史,就是平坦化的歷史。對嵌入孔内的要求,與要求膜的成品要很平坦,這是不可能同時實現的。為了嵌入而做了順形成膜(Conformal deposition)後,成品必定會有凹凸。如果採用電鍍,就能像上述那樣以Bottom up的方式來嵌入。如果只有微細孔洞,尚且能嵌入且維持平坦,但如果混雜著許多不同型態的狀況,那就很難處理了。

成品的電鍍膜厚度若分布不均,後工程的CMP就很難處理。所以電鍍製膜製程當然希望能盡可能平坦。

# 各種平坦化電鍍製程

從過去到現在,業界已經開發出許多平坦化的電鍍製程,但是卻沒有任何一個方法被採用過。為什麼?為了達到平坦而使用許多藥劑或研磨,結果反而對完成的膜質帶來負面影響(這裡說的是講自己實驗的結果,而非其他公司)。

那麼可不可以不放藥劑也不研磨就達到平坦? 我想到了下面這個點子。

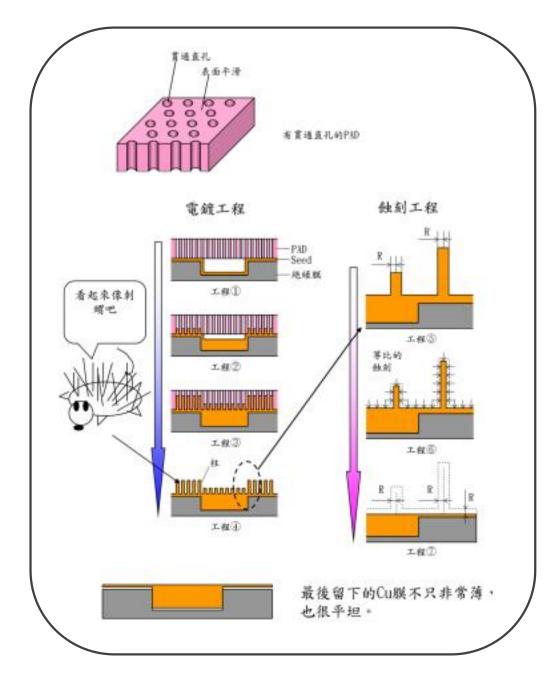

# 刺蝟製程

製程工程如圖所示。簡單來說就是在要電鍍的晶圓上,放個多孔的墊片(PAD)後 再電鍍。在沒有孔的地方不會有太多電鍍材質,只有晶圓的孔(想電鍍的地方)與墊 片的孔才會成膜。

在這個墊片孔內,因電鍍形成的針狀膜(很像刺蝟)可以以蝕刻簡單地去除。當然此時蝕刻的加工範圍要限制在不會損傷到配線部的電鍍層。最後留下的Cu膜不只非常薄,也很平坦。這個技術目前還在開發階段,但如果研發成功,CMP就變得非常簡單,且平坦化的能力也會獲得改善,可望成為32nm製程以後的革命性技術。

64

實際應用例

# 高熔點金屬封蓋電鍍

.....

### 金屬封蓋的目的與規格

金屬封蓋 (Cap metal) 的目的與規格如下所示:

- (1) 首先,因為它是配線的一部分,因此低電阻是第一個必要條件。

- (2) 為降低有效介電常數,僅在配線部位鍍膜。意即盡量避免使用Si-N等無機材質的 封蓋(這個目的目前仍未達成)。

- (3) 以防止EM (SM) 發生為目的。這是因為阻隔膜的Ta-N原本是它與絕緣膜的密著層,因此它與Cu之間的密著性差。故在此處發生EM (Electro Migration)與SM (Stress Migration)的可能性很高。因此,以透過高熔點金屬來提高密著性,藉以提升對EM與SM的耐性為目的。

- (4) 如果能改善與Cu之間的密著性,當然經由這個表面所產生的漏電(leak)也能得以降低。

- (5) 可在進行絕緣膜蝕刻時當做保護層。

封蓋的規格會依據以上種種目的來決定,目前仍有各種封蓋正在開發當中。例如W、Co-W、Co-B等材質。

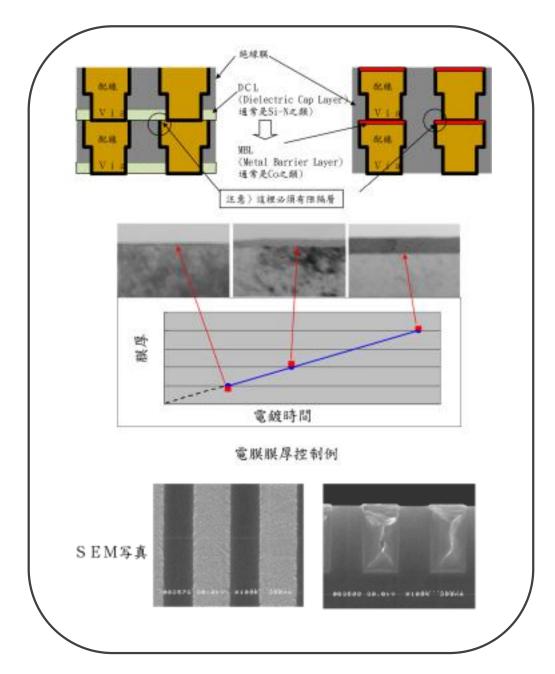

### 無電解電鍍Co封蓋

最近發表的論文中,大多是以提升EM耐性為目的。在提升EM耐性上,有使用Cu合金與未來的CNT(碳奈米管)等解決方案,甚至還有使用Co-W封蓋膜,EM耐性提升了100倍的報告。

Co在實際上鍍膜時厚度大約在5~10nm,右圖是鍍膜5~20nm時線性控制時間的例子。在 進行無電解電鍍時,只要嚴格控制電鍍槽溫度與流動,這種程度的控制是有可能達到的。

無電解技術的重點在於選擇性。如果想在銅配線上鍍上金屬封蓋,但又會殘留在絕緣膜上,就會導致可靠度變差。無電解電鍍原本就是以無選擇性鍍膜為特點的電鍍加工法,所以如何讓這個無電解電鍍具有選擇性就是各家公司的技術了。SEM照片是以Co在Cu上與絕緣膜上選擇性鍍膜的影像。

66

依電鍍液種類不同,又有Co-W與Co-B等不同膜種。

# 凸塊電鍍

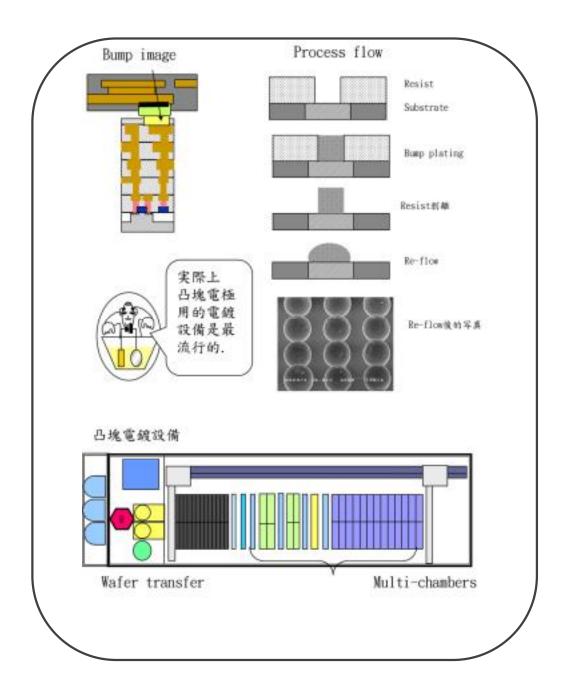

# 凸塊電鍍

晶片需要在終端部位製作與外部連接的電極,這個電極被稱為凸塊(bump)。 其截面圖如圖所示。

凸塊的製作流程如圖所示。簡單來說就是先以resist決定凸塊位置,讓電鍍材料 嵌入resist内。之後拿開resist回焊(reflow),就會形成如圖所示的凸塊。材料大多 使用黃金,以電鍍鍍膜。

凸塊的大小隨著晶片世代不同而有各種不同尺寸。大可到100μm角,小則可小到約50μm角的尺寸。根據發展進程,未來甚至能縮小到10μm角左右的程度。

而與其競爭的技術也很多。如印刷法,還有先將凸塊製成球狀後再放到指定的孔 内的方法。每個方法都兼顧傳輸量、精準度與成本,所以目前在技術上的競爭非常激 烈。我想最終,是符合微細化要求與適合微細孔的方法會勝出吧。

# 裝置圖

多槽電鍍設備圖如圖所示。電鍍配線時雖然只有鍍銅槽,但在凸塊電鍍接近完成的時候,由於關係到晶圓的潔淨度,故須進行①電鍍前表面處理、②清洗、③電鍍材料:鍍膜後電鍍數種膜、④洗淨後結束的過程。此時由於電鍍時間長,所以一般會設置多個電鍍槽來增加電鍍量。因此相較之下,電鍍凸塊的裝置流程會都有比較長的傾向。

# 電鍍裝置、鍍膜廠

那麼,做電鍍的是誰呢?有的晶片廠是自己做,也有很多叫Bump house的公司專門承包凸塊製程。

在晶片封裝上的電鍍並非稀有製程。晶圓製程中的凸塊電鍍雖然與晶片的封裝不同,但也不像多層配線那樣困難。可以說是介於多層配線與封裝之間的製程。事實上,晶片廠們也還在煩惱未來的10µm凸塊電鍍是要由後段製程負責,還是交給多層配線電鍍一併處理的問題。

# =MANABU風格:Power Point Paint派=

當我1974年進入荏原製作所(股)服務時,我負責印尼水力發電廠的建設。雙方正式商業用語都是英語,其實我那時的英文很差,根本就是美國西部片裡的印地安人。

「我,工程師。你,顧客。懂嗎?」我的客戶也是差不多的程度,真是部悲喜劇。我當時想照這樣下去發電廠還蓋得起來還真是奇蹟,但是最近想法改變了。我開始覺得英語不行其實對工程來說反倒是個好處。為什麼?因為英語不好,所以當然就「沒辦法說謊」。再來是如果想要傳達想說的話,因為是想要說的事情,所以會不斷強調講好幾次。而且講到對方懂為止。結果身為一個工程師,卻用畫畫的方式來傳達想說的事,擷取事物本質的訓練也是在這個時候訓練出來的。

那當時半導體製造設備的開發又是什麼樣子呢?就用繪畫來表達我想傳達的事吧。沒想到這一畫就瞭解了開發的本質了。之後我做工作時總是從「塗鴉」起頭。慢慢地連我寫的書也都加入了我的漫畫。在此提及個人私事雖然很不好意思,但其實我的姊姊是位「知名的」漫畫家(辻村弘子)。為了跟姊姊一較高下,我也用Power Point創出自己的畫風,就叫做「Power Point Paint派」(自創語)。不管是誰,只要來跟我拜師,馬上就可以學會如何畫漫畫唷(笑)。

# 第 III 篇 Wet Removal Technology: CMP 濕式削膜製程:化學機械研磨製程

### 從石頭 (石器) 到石頭 (晶片)

#### 世界最古老的研磨到最新的研磨 (CMP)

我在第II篇曾提到電鍍是世界最古老的技術之一,如果將電鍍比喻成西方的横綱,那麼研磨就是東方的横綱。確切的研磨技術起源可以追溯至磨製石器,是自繩文時代起即存在的技術(繩文時代是日本舊石器時代後期,大約是公元前14500年到公元前300年前後的時期)。另外,研磨基本上就是「互磨」,也就是使用氧化矽來研磨氧化矽。而在半導體晶片中,除了研磨氧化矽以外,還會需要研磨鎢與銅,但並非使用鎢與鎢或銅與銅互磨。如此看來CMP似乎已經跳脫出研磨的世界。不過,現今半導體晶片的平坦化技術仍舊以研磨為主要技術,未來想必會有更多研磨不同材料的需求吧。除此之外,半導體領域中所累積的研磨技術也能應用到舊有的研磨領域中,研磨的世界可說是希望無窮。

#### 半導體應用研磨 (CMP) 技術歴史概要

CMP是Chemical Mechanical polisher (化學的機械研磨裝置)的縮寫,目前是半導體晶片平坦化製程中不可或缺的裝置,由IBM於1980年代後期開發並用於「邏輯晶片用平坦化製程」中。由於邏輯晶片的層數較記憶體晶片多,因此對平坦化的要求也較高,又因為晶片生產數量少,成本也相對較高,所以應用在Off Line (無塵室外)的CMP比較容易獲得採用。其後美國的Intel、Motorola、AMD等公司也採用了此一技術。由於當時日本國内晶片廠的主要產品是記憶體,且已採用SOG(Spin On Glass: 旋塗式絕緣膜成膜法)或回蝕(etch back)等其他平坦化技術處理,因此並未採用CMP技術。此時期的CMP技術主要運用在研磨裸矽晶片的裝置,裝置本身的設計並未達到可以設置在無塵室內的無塵水準。為此,整套裝置必須設置在CMP專用的特別室,導致晶片製造廠遲遲難以正式採用這套技術。

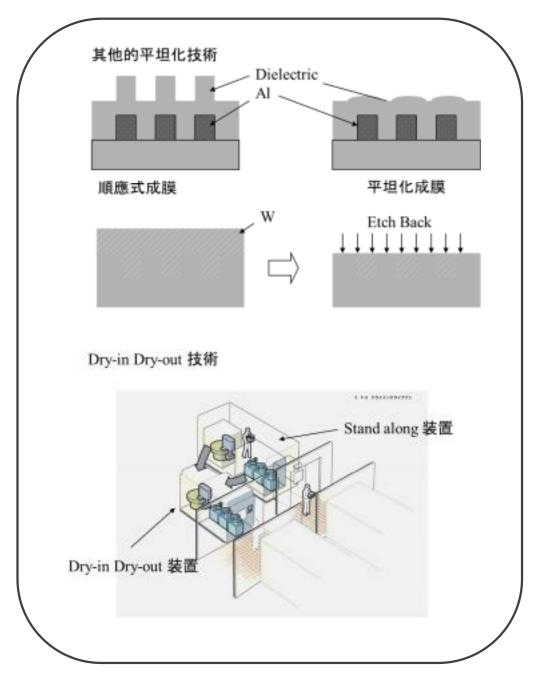

### Dry in、Dry out 登場

### 其他平坦化技術

在這時期内與CMP競爭的平坦化技術主要有以下幾種。

#### [層間絕緣膜平坦化]

- (I) 對晶圓施以偏壓射頻 (RF Bias) 進行成膜的偏壓CVD法。

- (2) TEOS與O3等具流動性的熱CVD法。

- (3) 旋轉塗佈的SOG法 (Spin On Glass)。

#### [配線平坦化]

- (I) AI成膜後加熱使其流動之方法。

- (2) 採用W等沉積技術 (Blanket CVD) 在成膜後回蝕的方法。

以上每個方法皆為1980年至1990年代前半應用於Technical node 350nm到250nm之間的技術,待鑲嵌製程(Damascus (大馬士革) 製程)出現後才逐漸轉為採用CMP。

#### Dry in, Dry out

1990年代起,隨著半導體對微細化的要求愈發嚴苛,日本也開始注意到CMP技術。CMP的設計概念在這個時期有了重大的改革。那就是Dry in、Dry out的概念。

因為採用此概念的設計,使CMP得以跟其他乾式製程裝置一樣設置在無塵室內使用,CMP因而變得更容易推廣普及。當時的層間絕緣膜平坦化技術主要為200mm (晶圓徑) / 250nm (Technical node) 世代,至此終於要迎接300mm / 130nm的新世代了。

這個新世代在技術需求上的最大特徵,在機械方面是全面導入已然意識到300mm世代來臨的「Dry in、Dry out」概念;在製程方面則是導入著眼於130nm世代之後發展的STI(Shallow Trench Isolation,淺溝槽隔離)、鑲嵌銅配線與低介電常數材料等要素,藉以達到製程多樣化。CMP遭受歧視(研磨等於骯髒)的時代自此宣告結束,於此同時,CMP製程與機械性能上的要求也一併變得比其他乾式製程要來得高。在被視為晶片與裝置開發的全球標準藍圖(ITRS)中,也將CMP列為打造下世代晶片的必備技術,CMP自此開始廣為世界悉知。

### CMP是毒品?!

••••••

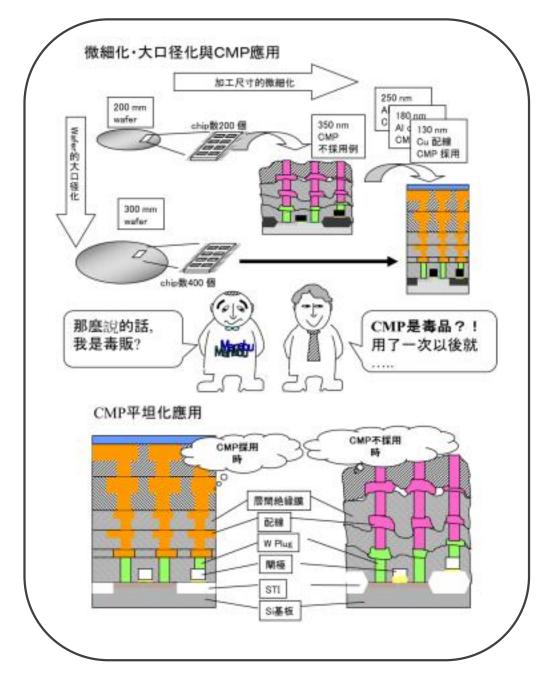

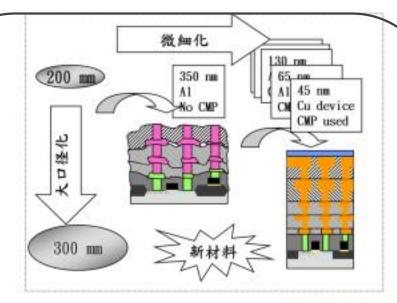

#### 微細化、大口徑化與採用CMP的示意圖

右圖說明CMP隨著半導體微細化與大口徑化而改變運用演變過程。CMP的運用始於200mm晶圓時代中的部分350nm世代晶片,於250nm世代晶片開始廣泛普及。在之後的微細化方面,則被視為必備技術。由於300mm晶圓時代沿用了200mm晶圓製程技術,CMP因而同樣不可或缺,應用於130nm世代的晶片上。

而在45nm世代之後的晶片上,CMP則運用在層間絕緣膜平坦化、鎢接點嵌入、STI嵌入、多晶矽平坦化、銅嵌入等各種製程中,現今則成為最先進晶片製造的必要技術。

#### CMP平坦化效果與其他用途

右頁下圖為CMP技術採用與否的晶片平坦度之示意圖。隨著配線多層化,各層的平坦化也愈趨重要。在其他用途上,CMP其實還具有提升表面改質效果的用途。例如可以磨掉殘留在各層的結粒(突出),或改善僅以純水研磨時帶來的洗淨效果等,CMP技術本身可以有許多不同的應用之道。

#### CMP是毒品?!

抱歉,我用了比較聳動的比喻。這句話是實際開始採用CMP的工程師所說的珍貴話語。1990年代前期,當時CMP尚未普及,那是個人們對CMP抱著「CMP?那個骯髒的製程?」的印象並敬而遠之的時代。一邊嫌棄一邊稍加嘗試後才發現「咦!跟想像的完全不一樣耶。雖然表面很髒,但髒污卻不會跑進晶片內部,而且平坦化性能可說是『出類拔萃』啊。」說出這句話的工程師,在一年後成了CMP技術的頂尖工程師。

他大膽斷言,現在如果沒有CMP,就做不出晶片。開頭那句話就是他當時所說的話,現在仍記錄在我的日記中。

半導體製造製程中研磨(CMP)扮演的角色是?

### 從 Preston 開始吧

#### Preston的算式

以下說明CMP的原理。傳統上CMP是用於裸矽晶圓研磨加工之應用。接下來以一般採用的旋轉式CMP說明。

將晶圓以Face back狀態 (表面向下) 固定於承載盤。接著在設置於旋轉台上的研磨墊上塗上研磨液 (Slurry,含有幾個百分比的二氧化矽等研磨粒的研磨液)。晶圓會夾在包覆材料與研磨墊之間,以承載盤壓向研磨墊進行研磨加工。此時旋轉台與承載盤朝同一方向以幾乎相同的轉速運轉。研磨速度和負重與相對速度成正比。

研磨的關係如下列Preston算式所示。

PR=kPV

PR: 研磨速度 (m/s) 、k: 常數 (Pa-1) 、P: 研磨壓力 (Pa) 、

V: 相對速度 (m/s)

維持固定研磨壓力的巧思,就在研磨頭的設計上。如果研磨盤與晶圓朝同一方向以同轉速旋轉,則研磨速度在晶圓上的任一點皆為固定值。

#### PVT依存與PVTQ依存

而對於化學性強的研磨液,其研磨速度也會受到溫度影響。此時研磨速度要修正 為以下算式。

$PR=kPVT^{\alpha}$

T: 研磨時的溫度 ( $^{\circ}$ C) 、 $\alpha$ : 溫度指數

又,近來為了達到降低CoC (Cost of Consumable) 的目的,研磨液流量有減少的趨勢,此時研磨速度可能會依研磨液流量而改變。在此情況下,研磨速度要修正為以下算式。

PR=kPVT¤Q₽

Q: 研磨液流量 (m3/s) 、β: 流量指數

Preston 算式與其應用式就像這樣實際運用在各個製程當中。

### 這就是研磨!

•••••

#### 簡述平坦化原理

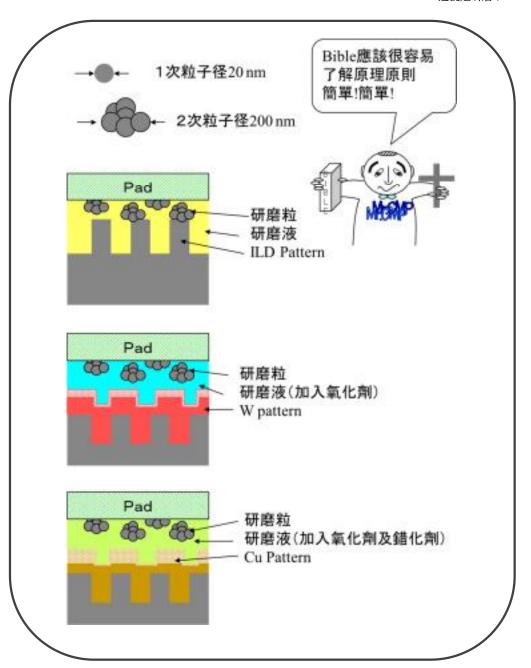

先來簡單說說研磨。嚴格來說這樣並非完全正確,但剛入門時這樣講比較好懂。 CMP是由Chemical (化學性要素)與Mechanical (機械性要素)組合而成的Polish加工。那我們來想想看,什麼是化學性?什麼是機械性?

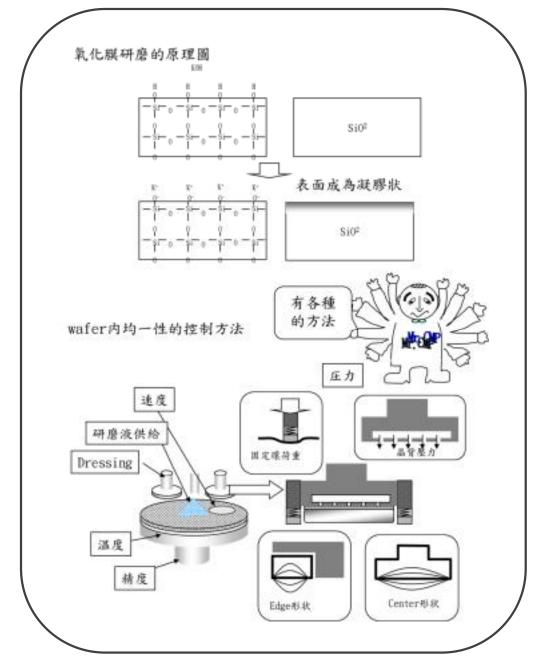

#### (1) 氧化膜

Si的氧化膜以SiO<sub>2</sub>表示,基本上就是研磨粒(SiO<sub>2</sub>)互磨(以相同材料摩擦加工)。 因為是相同材料,所以不容易造成損傷。先以鹼進行表面改質(化學性),再以研磨 粒將該表面層除去(機械性)。

SiO<sub>2</sub> (研磨粒SiO<sub>2</sub>+鹼性研磨液) → SiO<sub>2</sub>↑

#### (2) 再來是金屬鎢

此時若以研磨粒加工W等純金屬,即會造成損傷(因為金屬過軟或沾黏)。所以要先讓W的表面氧化,再施以與SiO2研磨時相同的機械加過程。這其中的氧化就是化學性,加工即為機械性。

W+氧化劑→WOx↑

#### (3) 最後是Cu

基本上過程與W相同,但是Cu與W為不同金屬,其氧化膜並不堅硬。讀者可將之想像成會漸漸腐化的感覺即可。因此,處理Cu的方法並非讓其產生氧化膜,而是使Cu產生錯合作用後再進行機械加工。此段過程即是讓Cu一邊氧化一邊轉變為錯合物。此作用為化學性,而錯合物的加工則是機械性。

Cu+氧化劑→ Cu<sup>++</sup> (非CuOx, 使其離子化也會氧化) CuCu<sup>++</sup> 錯合劑→ Cu (錯合物)↑

### 奇怪! 違反 Preston 算式?

### Preston領域與非Preston領域

遵守Preston的算式的研磨稱為Preston領域,但最近也出現了脫離這個理論的研磨方法。這些研磨方法稱為非Preston領域,主要使用化學性較高的研磨液。簡單來說就是蝕刻力高的方法。

研磨包含化學性要素與機械性要素。要以哪一個為主? 化學反應與機械加工是否能涵蓋整個 晶圓,並對晶片內進行均等加工?這些思考就是CMP技術。

#### 簡述性能

一般來說半導體製造裝置的性能有Process性能與機械性能。

評估Process性能的要素有:

- ·加工率

- ・晶圓整體均一性

- ·晶片内均一性(成膜與削膜的圖案依存性)

- ·Defects (雜質或傷痕等)

機械性能(以上述Process為前提)

- · 處理性能 生產率(throughput) (wph) 與作業時間(tact time) (hr)

- ·可靠性

- · 生產性指數

而CMP也是依照一般常識評估。以下針對CMP的狹義要求追加說明。

#### 評估項目

- (I) 速率: 當然是越快越好,不過有個大致的標準是以1分鐘的Process來評估。也就是說,假設一分鐘處理膜厚1µm,那就是1µm/min。評估標準大致如下:

- ① ILD > 500 nm/min (有時候是1,000 nm/min)

- ② STI 200 nm/min

- ③ W 500 nm/min

- 4 Cu > 500 nm/min

- (2) 均一性 (晶圓内): 以Beta晶圓驗證 在3 (2) mmEE下3σ3% 機械性要素高的氧化膜研磨製程,其研磨頭的性能將直接影響效能。而化學性要

奇怪!違反 Preston 算式?

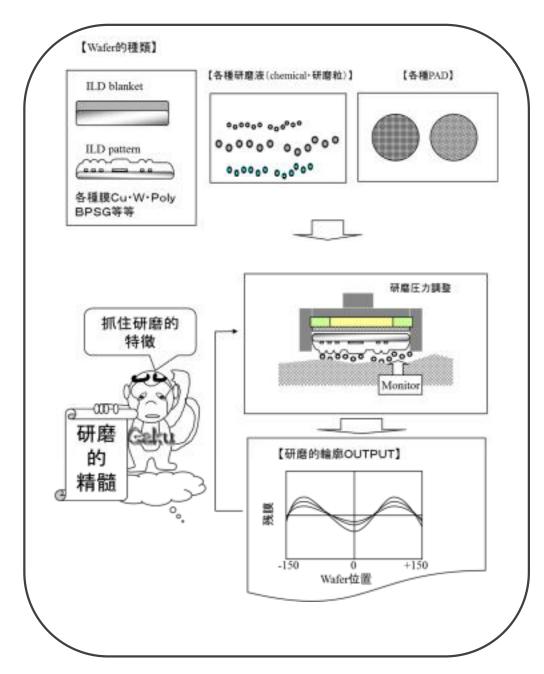

### 傳授研磨的精髓吧

••••••

#### 研磨慣性?

在這裡要注意了! 研磨就算平均施加荷重也沒辦法平均加工嗎!?

〈原因-1〉研磨會因被加工物──晶圓圖案的形狀 研磨液和研磨墊的不同而導致基本加工形狀不同。此基本加工形狀叫做「研磨慣性」,要修正這個研磨慣性就必須控制(改變)研磨壓力,加工出一致的研磨形狀,這就是研磨的精髓。

<原因-2 > Incoming Wafer 的形狀常常不同,因此便有控制此形狀的需求。這種技術稱為研磨的輪廓控制(Profile control),但如原因-1所述,研磨本來就有輪廓控制,所以Incoming Wafer的形狀就算有點變形也是可以調整的。

所以,目前CMP一般來說是依據晶片圖案、研磨液、研磨墊的種類,加上適當的 研磨壓力控制來獲得預定要有的性能。

#### 其他變動主要因素

在上述的研磨特性中,原本就包含著許多影響研磨的變動因素,必須特別注意。 在此簡單說明這些變動的主要因素。

例如修整器(Dresser)。研磨速度與形狀會因為修整器的種類(粗細)與修整方法等而有大幅變動。另外晶片的膜質也會造成很大的影響。例如以前會因BPSG膜B與P的分布或銅的退火溫度不同而變化,最近則是會依低介電常數的*蝕刻*損害不同而大幅變動,故必須注意。

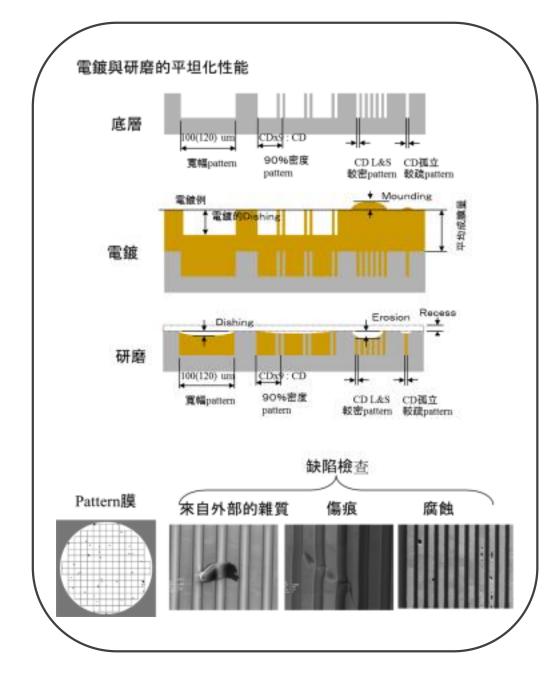

### 永遠的課題: Pattern依存性 (Pattern Dependency)

•••••

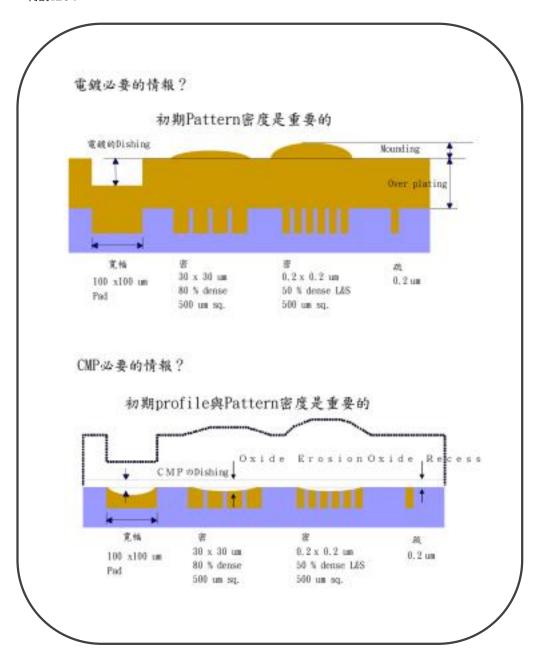

#### 平坦化性能 (Dishing、Erosion等)

晶片內會因為配線圖案 (wiring pattern) 而有凹凸疏密,若將膜製於其pattern 上,則不管用什麼成膜方法都會出現pattern依存性。這種現象稱為成膜的pattern 依存性。若接著進行磨削,其形狀也會有依存性,這現象稱為削膜的pattern依存性。

如圖所示,在寬幅pattern、較密pattern、較疏pattern上進行電鍍時,會有① 電鍍製程中產生Dishing、②較密pattern上隆起Mounding等特徴。

若以該狀態繼續進行CMP,會發生①寬幅pattern因CMP產生Dishing、②較密 pattern容易發生的氧化膜Erosion、③整體過研磨的Recess等現象。

注)不管在成膜、削膜或表面處理,都會面臨相同課題。這個課題就是pattern依存性。晶片有許多種pattern,會有pattern依存性的製程怎麼樣就是沒辦法改善。只能盡可能開發pattern依存性較少的製程。

#### 缺陷Defects - 含FM (雜質)、PS (傷痕)、PR (研磨殘留)等類別

要使用什麼檢查機來檢查什麼,是進行缺陷Defect檢查很重要的一環。現今實 務運用中的檢查機有以下幾種:

- ① Blanket膜上的雜質檢查機

- ② Pattern膜上的缺陷檢查機→如上所述,可分辨雜質、傷痕、腐蝕等。分暗視野與明視野,兩者原本皆為必要。

86

#### 類別上有:

- ·來自外部的雜質 FM (Foreign materials)

- · 傷痕 PS (Polish scratches)

- ·研磨殘留 Polishing residue

- ·腐蝕 Corrosion

- ・侵蝕 Erosion

各家公司有其個別的稱呼。

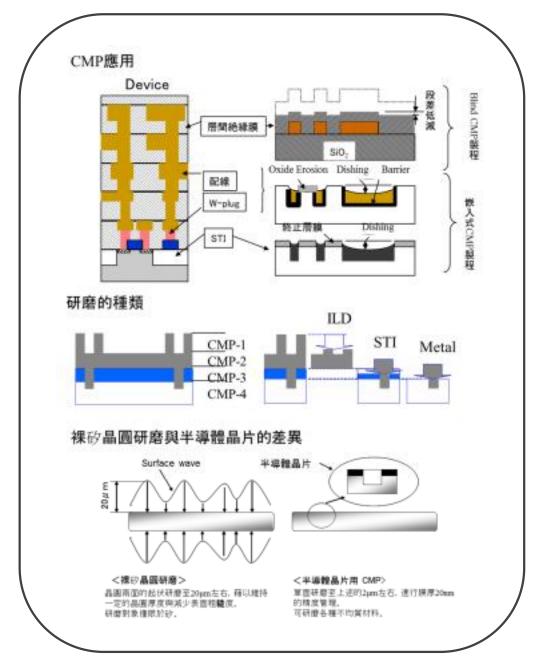

### 用在晶片的哪裡?

CMP適用處

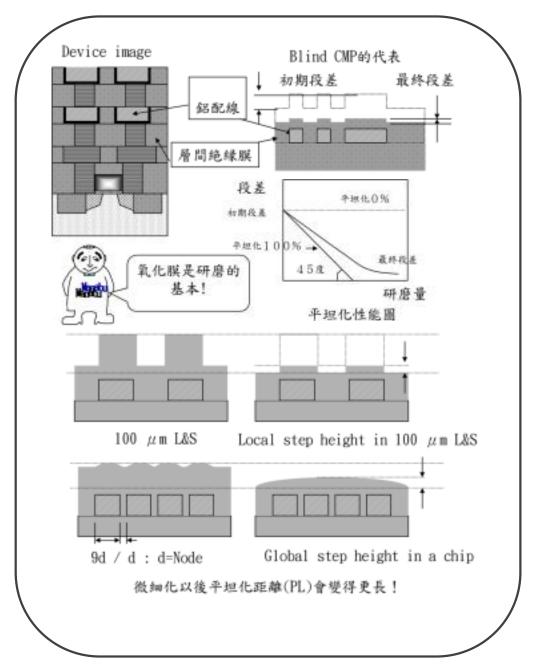

適用CMP加工的位置如圖所示。圖中可見STI、各層層間絕緣膜(ILD)、鎢栓塞(W plug)與各層金屬,以CMP的角度來看,又可粗略分為沒有CMP終止層(stopper layer)的「Blind CMP製程」與有終止層的「嵌入式CMP製程」(Recess CMP)。層間絕緣膜的研磨採用均質膜的Blind CMP製程,主要要求在於降低段差的能力。STI採用有Si-N等材質終止層的嵌入式CMP製程,主要要求在於提升終止層內的均一性及降低Dishing。配線層則採用含阻隔膜的嵌入式CMP製程,主要要求降低Dishing與Oxide Erosion。Dishing是指配線部分出現像盤子一樣過研磨的現象,而Oxide Erosion也同樣是配線間氧化膜過研磨的現象。

#### CMP的四個階段

如上所述,材料有氧化膜(ILD與STI)、金屬(W、AL與Cu),以及其他PolySi等材料與用途,但這裡我嘗試以研磨性質區分Blind CMP的ILD,與Recess CMP中的STI、W與Cu。

- ·CMP-I 減少高低差區域 (ILD) 被加工材料為同質 = 以降低高低差為主。

- ·CMP-2 塊體 (Bulk) 研磨區域 被加工材料為同質 = 以晶圓均一性為主。

- ·CMP-3 異質材料區域 (Recess的終止層或阻隔膜) = 以選擇比為主。

- ·CMP-4 基底材料區域 = 以Defect為主。

另外實作上還有「CMP-0」階段。剛開始研磨被加工材料的氧化膜時,常會發生問題,如果材料是Cu,則研磨Cu之前必需先研磨CuOx。

#### 裸矽CMP與晶片CMP的差異

以下介紹傳統裸矽晶圓研磨與半導體晶片CMP最大的差異以供參考。裸矽晶圓的研磨是將晶圓兩面的起伏研磨至20µm左右,藉以維持一定的晶圓厚度與減少表面粗糙度。當然,研磨對象僅限於矽。而半導體晶片CMP則是將單面研磨至上述的2µm左右,進行膜厚20nm的精度管理並可研磨各種不均質材料。裸矽晶圓研磨製程與半導體晶片CMP製程雖然相似,但卻也大大地不同。

### 研磨部、洗淨部

所謂CMP系統是指包含研磨、洗淨、乾燥、監控、研磨液供給、廢液處理、研磨 墊、研磨液等階段與材料,再加上管理技術、自動化技術等技術的一整套系統,但這 裡只抽出主要的研磨、洗淨與監控技術來說明。

#### 研磨部

裸矽圓研磨始於80年代,幾乎都是採用旋轉的方式進行。當時相繼出現了許多重視生產率(throughput)的多研磨頭與多平台機種,至於性能那就不用提了。到了90年代,隨著微細化的發展,產品對於平坦化的要求也越來越高,為了提升易控制性,單研磨頭的裝置較受大眾歡迎。那同時也是個出現多種研發機種的時代。

- (1) 小工作臺型: 為了節省空間,將晶圓配置在超過旋轉工作臺中心的位置進行研磨。就幾何學上而言就算超過中心,晶圓上的滑動速度仍可維持一致。

- (2) 小研磨頭型: 使晶圓朝上, 以比晶圓小的研磨頭進行研磨。

- (3) 線性型: 研磨墊採直線運動而非旋轉。

- (4) 磨削型:採磨削原理而非研磨進行平坦化。

- (5) 固定研磨粒型:採固定而非游離研磨粒進行研磨的方式。

#### 洗淨部

80年代、不,即使到了90年代,還是沒有人想到要把洗淨功能內建到CMP系統內。研磨可是灰塵的製造機。而洗淨設備是所有半導體製造設備中最不能容許灰塵的設備,在那個時代要將灰塵製造機與清浄機放在一起,那簡直就像是要把天與地放在一起一樣。實際上,在化學工程製程中並沒有將10<sup>15</sup>的粒子降到10<sup>9</sup>等級的分離製程。所以只能依靠傳統浸泡式RCA洗淨法。之後隨著CMP系統的採用次數增加,當然也就出現了希望CMP可以與其他乾式裝置一起並列使用的想法。於是到了90年代,所謂的「Dry In、Dry Out概念」便因此產生。其後還出現了縱式與單槽式(One-bath),以及為達成:無化學"目標而被運用的Functional water例如臭氧水或離子水等。

91

### 監控部

#### 監控的種類

研磨製程大致上分為兩種。一種是研磨如ILD均質膜的Blind Process,另一種則是磨削如W、Cu、STI等非均質膜的嵌入製程。目前實務上已有許多配合這些製程而開發出來的監控系統。

- (1) 摩擦檢知方式:透過設置於平台或研磨頭上的力矩檢知器,偵測發生於非 均質膜邊界的力矩變化。多用於W等製程上。監控電流式也包含在此類別 中。

- (2) 振動檢知方式:透過設置於研磨頭上的振動加速度監控器,偵測發生於非均質膜邊界的振動加速度變化。

- (3) 渦電流檢知方式: 透過隨金屬膜厚度變化的渦電流來監控膜厚變化。應用 於金屬嵌入CMP製程中。

- (4) 光學式檢知方法: 與光學式膜厚監控原理相同。分為In-line式與In-situ式。

- (5) 其他: 偵測研磨非均質膜之際發生的特別化學反應或聲音變化等, 各式各樣的方法皆正在研發當中。

#### 實際數據比較

右圖為實際採用的馬達電流式、振動式與渦電流式的例子。馬達電流式為最早開始使用的方法,此方法透過旋轉力矩來偵測非均一膜質間產生的摩擦力。振動式是透過設置在研磨頭的振動傳感器來偵測非均一膜質間產生的振動模式差異。右圖為馬達電流式與振動式偵測相同晶片圖案所得到的結果比較。而渦電流式的方法則是運用金屬內產生的渦電流大小會因金屬厚度而產生變化的原理來偵測。圖例為研磨Cu與Ta時的例子。

# 監控部 電流Monitor 振動 膜厚測定 音響 Chemical 光学式 磁気 缺陷検査装置 各種比較 振動式\* 被勢強 渦電流式 馬達電流式 研磨時間(位置) 研磨時間(位置) 参考研磨位置面

半導體製造製程中研磨(CMP)扮演的角色是? Raw Process Time

#### **Raw Process Time**

.....

#### Raw Process Time改善

In-Process Monitor的主要目的是監控研磨停止資訊與膜厚管理資訊,但除此之外還包含了故障診斷、壽命預測或縮短Raw Process Time (實際處理時間)等功用。以下也針對研磨系統的 In-Process Monitor做說明。

- (1) 研磨停止資訊 (Endpoint): 如前述,由於CMP不是精準加工機械,所以需要Endpoint 相關技術輔助。其中一個方法是本書所提到的機械性停止,此外也有開發會自動停止的研磨液與研磨墊的研究方向。不管是哪一個,都必須開發適用於88頁CMP四領域的Endpoint。

- (2) 膜厚管理資訊: 層間絕緣膜的膜厚會大大影響晶片性能。進入Low-k時代後, 其管理幅度想必會越來越嚴格吧。因此, 從單純的Endpoint來進行膜厚管理也是必然的目標。

- (3) 故障診斷、壽命預測:由於CMP是可靠性與重現性差的製程,Endpoint的開發也因此急速升高。但其實其可靠性與重現性也有某種固定模式,這些資訊可透過調查研磨停止資訊與膜厚管理資訊獲得。例如透過比較一般正常的研磨停止資訊與膜厚管理資訊,即可應用到故障診斷與壽命預測上。

- (4) 縮短Raw Process Time: 右頁上圖所示的內容為研磨、洗淨、終點監控 (EPD) 各別獨立設置以及分別內建洗淨及EPD後, Raw Process Time縮短的幅度。現在的All-In-One型與傳統的獨立型相比, Raw Process Time縮短為過去的三分之一左右。另外,由於研磨在整個製程時間內的比例提高,過去通常傾向省略的前導測試晶圓 (Leading test wafer) 也變得較容易採納。

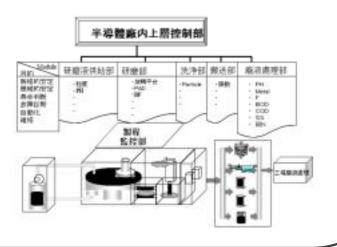

#### 其他管理資訊

另外,下圖還列出了CMP系統中包含研磨、洗淨、運送、研磨液供給、廢液處理的管理方法範例。這些項目透過上層通訊,是會大幅影響工廠營運的重要項目。In-Process Monitor並非只有研磨製程中才需要用到。舉例來說,刮傷(Scratch)與研磨液供給裝置的性能有很大的關聯;Particle數與洗淨裝置或運送裝置有關係;研磨慣性也會因耗材不同而大大地改變。此外,往後研磨新材料時,如何減低包含廢液處理在內的環境負擔也是業界必須面對的課題。

### Raw Process Time改善

#### 上層通信例

### 研磨液再生與廢液處理

#### 研磨液

研磨液的性能是依「研磨粒與研磨液及被研磨膜之間的機械加工性與化學反應性」來決定。對於氧化膜,目前業界主要採用KOH基或Ammonia基的二氧化矽(Silica)研磨粒 二氧化鈰(Ceria)、錳類(Manganese)研磨粒、評估項目有研磨率 刮傷(Scratch)、洗淨性。金屬膜則採用過氧化氫(hydrogen perozide-)、硝酸鐵(ferric nitrate-)、碘酸鉀基氧化鋁(potassium iodate-based alumina)、二氧化矽與錳類,評估項目則為上述項目再加上Dishing / Oxide Erosion / Corrosion。

而課題就在於配合金屬膜用的各種膜層、barrier film阻隔膜與underlying film 基底膜 維持必要的選擇比 並同時思考如何以低價且快速的方式開發出新的研磨液, 以利通過上述評估項目。

#### 研磨液供給系統

研磨液供給方式分有現場個別式(on-site supply)與集中式(central supply)。在實驗等級或需要頻繁更換研磨液的場合下,採用現場個別式比較適合,但實際量產的工廠則多採用集中式。另外,除了研磨液以外,電鍍裝置等其他濕式製程裝置的藥液供給也可採用同樣的作法進行。

#### 研磨液再利用與再生

目前,研磨液的成本很高,所以就有人想到要再生與再利用研磨液。如圖所示,所謂的再利用是指將使用過但尚未變稀的研磨液,透過過濾來循環使用。這是一般裸 矽圓研磨都會採用的作法。

而所謂的再生,則是指還原到原始研磨液的狀態。半導體用藥液已經有在現場再生的實務經驗,但研磨液就相當困難了。現階段而言,考量到環境問題,這當然是眾人希望努力開發的技術。

實際應用例

### 從ILD層間絕緣膜開始

#### 用途與平坦化性能的定義

ILD層間絕緣膜CMP是最先採用CMP的製程,算是CMP的代表。如圖所示,以組配線時,要在鋁上面以CVD製成氧化膜,所以會造成氧化膜有段差(step height)。即使採用前述成膜中的平坦化技術,但還是會產生段差。這種段差我們定義為初期段差。此初期段差經過研磨後就會平坦,但最後留下的差則定義為最終段差。從初期段差到最終段差之間,到底要研磨多少才好呢?這就是平坦化性能,其內容如以下算式所示。

平坦化性能 = (初期段差 - 最終段差) ÷ (研磨量) (若以%表示則×100) Planarization performance = (Initial step height – Final step height) ÷ (Polishing volume) (×100 if expressed in %)

圖中的45度線代表「研磨多少,高低差就減多少」,也就是理論平坦化100%。 圖中的平行線代表「不管怎麼研磨,段差也不會減少」,也就是平坦化性能0%。讀者 可以想像一下濕式蝕刻等技術。雖然這看起來像是理所當然的定義,但當我們討論到 電解研磨或其它平坦化技術時,這些定義就很重要,請牢牢記在腦中吧。

另外,絕緣膜成膜的嵌入性正在努力進行改良,目前已經大幅降低初期段差了。

#### 平坦化距離增大!

但是,改良了嵌入性卻帶來了副作用。當配線的Line&Space (L&S)較寬時,不管嵌入性多好,氧化膜還是有一定程度會沿著配線圖案成形;而要是L&S變窄,絕緣膜就沒辦法沿著配線圖案成形,導致配線圖案全部被埋住。

這個問題會為CMP帶來一個大問題。那就是該降低的段差幅度變得非常寬,甚至可能達到相當於晶片面積的I0mm程度!

這可以說已經進入到研磨技術難以克服的境界了。用專業用語來說的話就是PL (Planarization Length) 增大。解決方法呢? 我們繼續看下去。

98

### 以輪廓控制達到均一性

••••••

#### 削膜的原理

氧化膜SiO₂的研磨原理如下。

[化學性] 表面的羥基-OH因鹼的攻擊而形成凝膠層(gel layer)。

[機械性] 接著以機械性的方式去除此層。

#### 研磨速度與平坦化性能

氧化膜的研磨是CMP的基本,所以這裡我們再把Preston的算式拿出來用。

Preston的算式 PR=kPV

實際上這裡還要加上溫度作用 (Arrhenius的算式),

故Preston修正算式為 PR=kPVT<sup>cl</sup>

前面也提過各種研磨液與研磨墊的數據都必須確認PVT依存度。

平坦化性能則如前述:

平坦化性能=(初期段差-最終段差)÷(研磨量)(若以%表示則×100)

#### 晶圓内均一性

接下來說明晶圓內均一性相關參數與控制方法。如圖所示,一般來說,與晶圓均一性有關的參數為:

- 1) 下壓荷重 (pressing load)

- 2) 相對速度 (Relative speed)

- 3) 溫度 (Temperature)

- 4) 研磨液與研磨墊種類 (Slurry/pad type)

- 5) 平台的精度 (accuracy of table operation)

此處2) 到5) 為一定值, 而1) 下壓荷重的控制方法如下:

- 1) 晶背壓力控制 (backside pressure)

- 2) 固定環荷重控制 (retaining ring load)

- 3) 研磨墊的邊緣與中央的形狀控制

詳細内容請參照下一頁。

### 從後面、從旁邊、轉圈圈

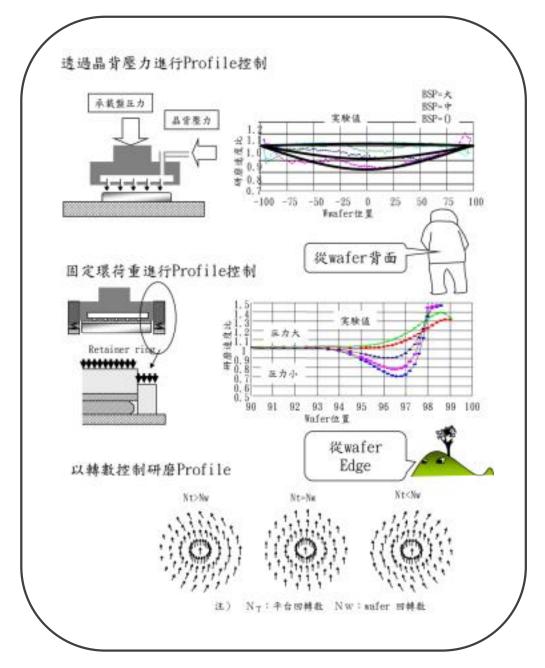

三大代表性研磨速度Profile(晶片表面的輪廓)的控制方法如下所示。

#### 透過晶背壓力進行Profile控制

圖為以晶背壓力控制進行Profile控制的例子。這是CMP初期便採用的方法。這個 方法是在承載盤上開數個孔,再從承載盤背面以流體壓力調整荷重的方法。由於這個 方法簡便又有效,目前仍使用於實驗機等設備上。

在CMP均一性要求還不高的時代,這個技術就已經足夠了。但是之後產品對均一性的要求越來越嚴格,此種裝置的性能也開始趕不上要求了。前面已經提到若使用研磨墊或研磨液等進行研磨時會有研磨慣性。要配合這個研磨慣性來調整孔洞的壓力,就會變得越來越困難。但需求就是發明之母,出現了需求後就有人在這方面下各式各樣的功夫。以下就是其中一例。

#### 固定環荷重控制

固定環是設計於晶圓周邊施加荷重的環。透過調整來自研磨墊的反彈力,可控制 晶圓邊緣的研磨速度。這個方法已運用於最新的CMP設備,也是第一個向世人展示不 可忽略研磨墊反彈力的例子。因為研磨墊的剛性與厚度會使得控制更加複雜。圖為以 FEM分析控制的例子與實際控制的例子。

#### 以轉數控制研磨速度

圖為以轉數控制研磨速度的例子。通常會藉由將平台轉數與研磨頭轉速維持在相 同速度,藉以同步晶圓與研磨墊間的相對速度。圖的中心為此時的向量。平台的速度 高於研磨墊的速度時為左圖,反過來則是右圖。藉由此方法即可控制晶圓邊緣與中央 的研磨速度。

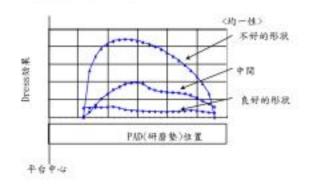

### Dressing、流量與振動

接下來介紹會讓晶圓內均一性變差的各種主要因素與其對策。

#### 透過Pad Dresser(研磨墊修整器)改善

如果不以Dresser控制研磨墊表面形狀,則均一性就會變差。圖為以各種Dresser 加工的研磨墊表面。由圖可知藉由Dresser的種類與修整方法,即可控制研磨墊表面。 要平一點、凸一點或凹一點,都可藉由當下的製程來調整。

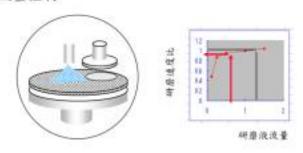

#### 研磨液流量控制

雖然大家都想盡量減少研磨液流量,但還是必須估計好減少的極限在哪。如圖所示,以前剛開始實際採用CMP時,研磨液用於維持研磨速度在一定範圍的情況。例如200mm晶圓,則標準約為200cc/m。300mm晶圓原本需要約400cc/m,但由於研磨液成本很高,所以目前仍在嘗試盡量減少研磨液的使用量。圖為研磨液流量對研磨速度影響的實驗結果。

#### 滯滑現象 (Stick-slip)

研磨的運轉條件有時會因為晶圓、研磨液與研磨墊種類而產生很大的差異。例如若是在比較容易固著(摩擦力高)的條件下進行研磨,則裝置可能會產生振動。造成這現象的其中一個原因可能是滑滯現象。讀者可以將滑滯現象想像成晶圓因為摩擦力而「卡住」。發生這種狀況時可進行振動分析並據此執行排除振動的對策,如此即可在寬鬆的條件下進行研磨。

### 透過Pad Dresser(研磨墊修整器)改善

#### 研磨液流量控制

滯滑現象 (Stick-slip)

對策後

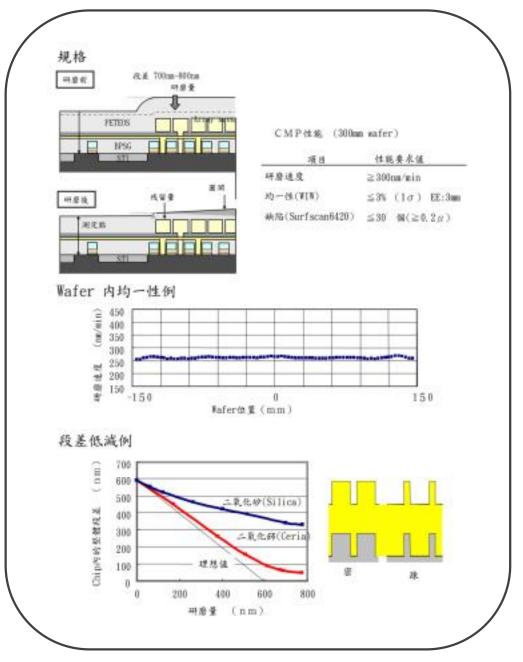

### 這就是ILD規格

••••••

接下來介紹層間絕緣膜ILD的規格範例。

#### 規格 (Specifications)

圖為一般的規格。

基本上有研磨速度、晶圓內均一性、平坦化性能、缺陷數等,其他還有Profile (輪廓)控制性等項目可依使用者的特定要求而追加。

#### 晶圓内均一性 (In-wafer non-uniformity)

一般晶圓內均一性如圖所示。

·膜 種: PE - TEOS

·研磨墊: IC1000-050 (K) / S400

·研磨液: SS-25 (1:1)

·平台與承載盤轉數: 70 / 70 [rpm]

實務上並須在連續測試中證明其安定性。

#### 研磨Profile控制性 (Polishing profile controllability)

有時製程會碰上需要修正研磨前成膜製程形狀的情況。此時便需展現出為此所準備的研磨Profile控制性。Profile控制的方法如前所述。

#### 減少段差的性能 (Step height reduction)

圖為代表性的二氧化矽研磨液與二氧化鈰研磨液(Silica & Ceria slurries)的減少段差的性能。此減少段差性能會受到晶片圖案的大幅影響。哪個地方比較難進行平坦化會受設計影響,故需要與研磨結果詳細對照。

實際應用例 STI CMP

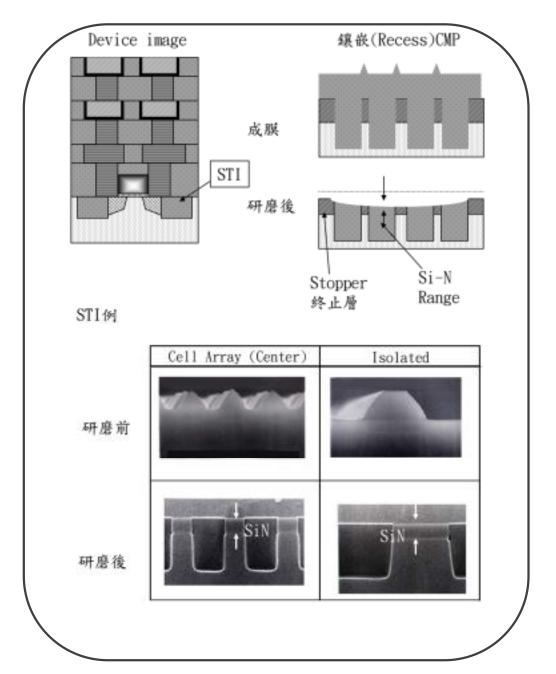

### **STI CMP**

#### 用途與課題

用途與性能如圖所示。而課題就在於終止層 (Si-N) 内的範圍與減少缺陷。照片 為研磨前與研磨後的狀況。

#### 原理

STI (Shallow Trench Isolation) 研磨大致可分為以二氧化矽研磨液與二氧化鈰研磨液進行的研磨。以二氧化矽研磨液進行研磨的原理與層間絕緣膜的研磨相同。

#### 晶片内均一性(In-Chip non-uniformity)

這是STI特有的需求,而有爭議的是用來當終止層的Si-N內的範圍。一般的方法是取較高的SiO2膜與Si-N膜的選擇比,然後不太研磨Si-N,並減少Si-N的範圍。取較高的Si-N選擇比就代表SiO2的研磨速度比Si-N的研磨速度大,故一般會產生(SiO2的)Dishing量變大的矛盾(trade-off relationship)。為了解決這個問題,過研磨的性能就變得很重要了。STI研磨的訣竅在於(1)Si-N對SiO2的選擇比要高,例如1比30、(2)即使過研磨也要讓SiO2的Dishing變少。

#### 缺陷 (Defects)

在STI研磨的世界裡,傷痕 (PS) 可以說是這裡的一切。一路貫穿到Si-N下方的 Killer傷痕當然是NG,但不管實不貫穿,最好SiO<sub>2</sub>上不要有任何傷痕。另外到達Si-N 前的傷痕的寬深比也是個問題。例如寬l0μm、深lμm的傷痕是否最後會轉印過去?還是會消失?這樣的問題是很重要的。轉印的話當然就是出局!也就是說這是10比lμm 的傷痕在之後是否能平坦化的問題。

#### 監控 (Monitoring)

具有高選擇比二氧化鈰(ceria slurry)的研磨可透過摩擦力進行終點偵測。

### 各種STI攻略法

以下介紹各種STI的研磨方法。我們究竟該如何徹底掌握STI呢?

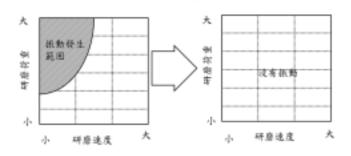

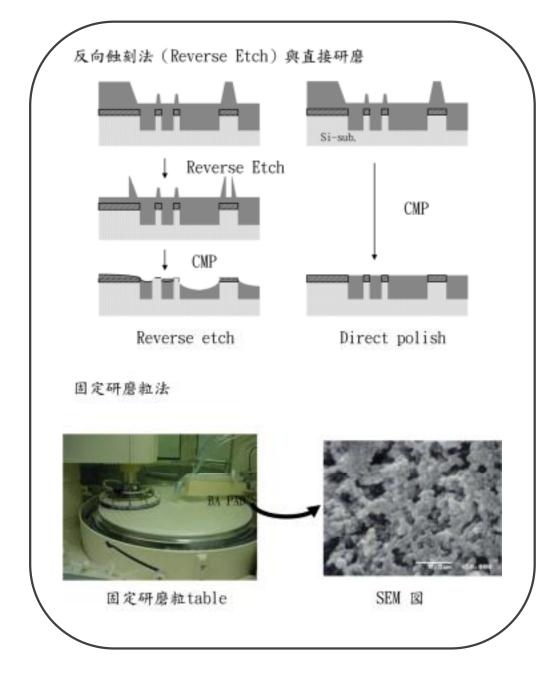

#### 反向蝕刻法 (Reverse Etch) 與直接研磨

一般來說如果不做任何加工而直接進行CMP, Field部較寬的時候不僅沒辦法達到平坦化, 甚至連終止層都有可能發生缺陷, 為了解決這個問題而想出來的方法之一, 就是反向蝕刻法。如圖所示, 反向蝕刻法是先在前工程階段蝕刻難以進行平坦化的 Field部, 再進行研磨的方法。透過這個方法可縮小所謂的平坦化距離, 讓平坦化得以實現。

#### 假鍍圖案 (Dummy Pattern) 法

假鍍圖案法是指在容易出現Dishing的圖案上事先加工假鍍做為門檻再進行研磨的方法。這個假鍍的配置與設計是晶片製造廠的技術與專利,因此在這裡我只點到為止。可以說的是,目前最先進的晶片製程裡就充滿了一堆這種假鍍。

#### 二氧化鈰磨粒法

那麼難道就沒有不用像上述方法那樣下功夫加工,就可以單靠CMP處理長距離的平坦化嗎?到目前為止有人加強研磨墊的剛性,有人提高研磨速度有效提升實質的研磨墊剛性。但這一切仍然不足,因此開始有人研究起以二氧化鈰研磨液(Ceria slurry)進行平坦化的方法。如今二氧化鈰法的運用非常普遍。

#### 固定研磨粒法

在提升研磨墊剛性的方法中,有一種是採固定研磨粒的方法。固定研磨粒有兩種方法,一種像3M公司那樣,將金字塔型的二氧化鈰固定在一般的研磨墊上;另一種則是製作固化二氧化鈰的研磨墊。右頁的照片是採用後者的照片。

固定研磨粒的課題是降低缺陷。

實際應用例 鎢 CMP

### 鎢 CMP

٠٠٠٠٠

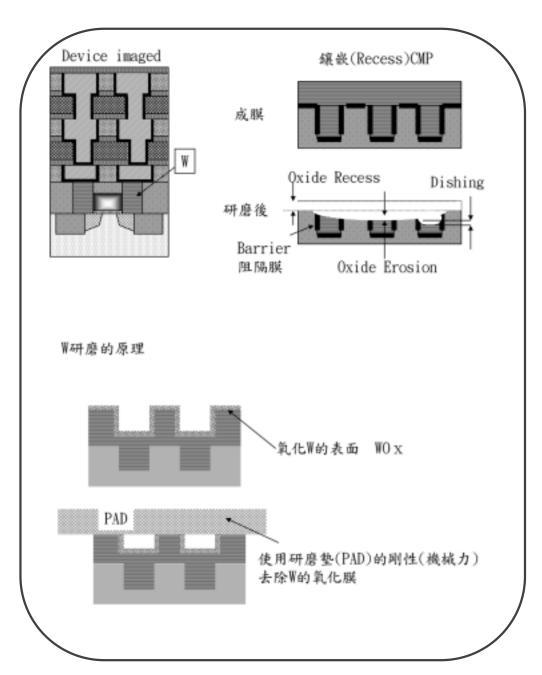

#### 用途與課題

鎢接點 (contact) 和通孔 (via) 的示意圖如右圖所示。絕緣膜為氧化膜,阻隔膜一般則採用Ti/Ti-N。故CMP為鎢→阻隔膜 (Ti/Ti-N) 的異種研磨,且為嵌入式CMP 製程。

規格需求如以下所示(依世代不同需求值也不同)。

· Oxide Recess: < I0nm

· Oxide Erosion : < 20nm

· Dishing : < l0nm

以課題來說,當然就是盡可能降低這些數值,而在製程上的目標是將鎢研磨與阻隔膜(氧化膜基礎)研磨及二種研磨液的兩階段CMP製程,融合成一次研磨所有材料的一段製程。就生產性來說,一段製程比較好,但就處理性能來說當然是兩段研磨比較好。一般認為要考量是哪一個世代的需求來決定是要採一段還是兩段。

#### 原理

鎢(W)CMP的原理如圖所示。

- (1) 首先以氧化劑氧化W的表面。氧化劑可用過氧化氫或硝酸鐵等。 W+Oxidizer → WOx

- (2) 接著以機械性方法去除W的氧化膜。此時是藉由研磨墊的剛性局部性地去 除突出部位來達到平坦化。

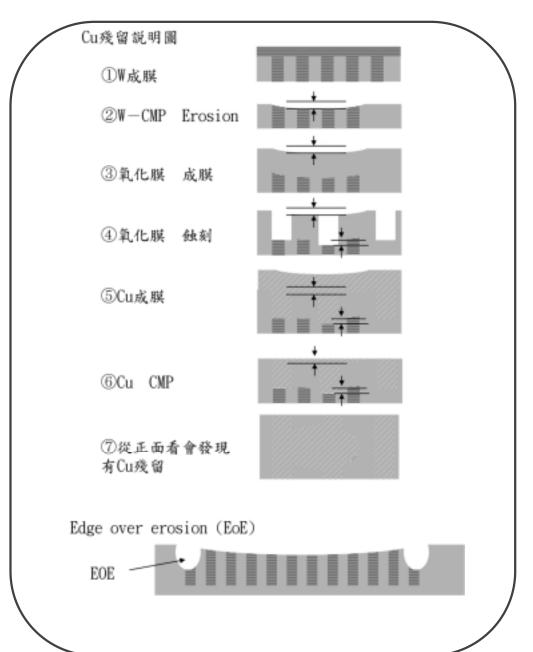

### Cu殘留是來自下層的W?

以下介紹鎢CMP最近掀起話題的兩個問題範例。

#### 因Erosion造成的Cu短路

由於鎢接點的CMP平坦性有可能造成在其上層的Cu配線短路,最近對於鎢CMP的平坦性要求也變嚴格了。以下以圖說明其中機制。

- ①從鎢已經嵌入接點孔成膜的狀態開始。由於鎢成膜是以CVD進行,故膜的成形可較為適形(conformal)。

- ②圖為鎢CMP中發生Oxide Erosion的圖。

- ③接下來依其Erosion形狀 (conformal) 形成氧化膜。

- ④接著將蝕刻高度也設為相同高度,則蝕刻形狀也會依Erosion形狀 (conformal) 而變化。

- ⑤之後在上面以電鍍成膜。此時如果忽略電鍍的Mounding等,則電鍍膜也會符合Erosion形狀(conformal)。

- ⑤ Cu研磨也會依著Erosion形狀研磨 (conformal) 。

- ⑦結果從上面看下來, Erosion的地方會有Cu留下來。

這就是受鎢CMP影響,使上層的Cu或金屬殘留下來的機制。解決這個問題的方法是盡量減少鎢CMP時的Erosion,以及將已產生的殘留部分以過研磨去除。

#### **EoE** (Edge over Erosion)

對於異種材料,若研磨選擇比大一點時,則可能會出現EoE,也就是大型針狀體 出現在邊緣附近的現象,但這個問題可以藉由調整選擇比解決。

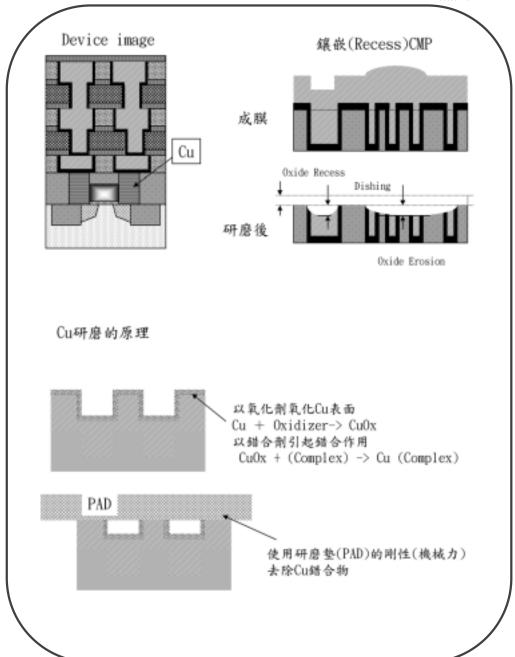

### 銅配線 CMP

••••••

在這裡我故意採用與說明鎢CMP相同的方式來說明銅CMP。由於同樣是配線的 嵌入製程,我想藉由比對,兩者的差異會更明確吧。

#### 用途與課題

右圖所示為Cu配線示意圖。絕緣膜為氧化膜或低介電常數材質(Low-k material), 阻隔膜一般為Ta/Ta-N或Ti/Ti-N。故CMP為Cu→阻隔膜Ta/Ta-N的異種研磨,且為 嵌入式CMP製程。

規格需求如以下所示(依世代不同需求值也不同)。

Oxide Recess : <10nm</li>Oxide Erosion : <20nm</li>

· Dishing : < 30nm (註) 因研磨墊較大, 此數值也較大。

與鎢相同,以課題來說,當然就是盡可能降低這些數值,但Cu研磨卻是以兩段或 三段研磨為主流。由於採用低介電常數,包含Damage在内的平坦性要求也越來越嚴 格。低介電常數等性能要求將在後文說明。

#### 原理

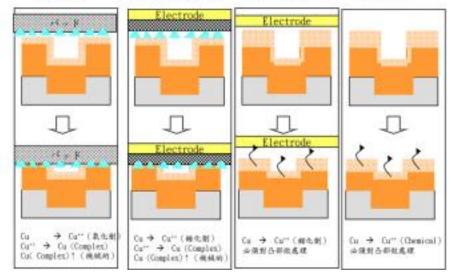

Cu CMP的原理如下所示。

- (1) 先以氧化劑氧化Cu表面 (價數增加)。

- (2) 接著將氧化後的Cu表面 (立刻) 以錯合劑引起錯合作用。

- (3) 以機械性方法去除Cu錯合物。此時藉由控制研磨墊的剛性選擇性去除突出 部位。

- $\cdot$  Cu $\rightarrow$  Cu $^+$  + 2e $^-$

- $\cdot O_2 + 2H_2O + 4e^{-} \rightarrow 4OH^{-}$

- · Cu + Complex $\rightarrow$ Cu (Complex)

- · Cu (Complex) ↑

關於Cu CMP之詳細内容請參照平坦化統一論。

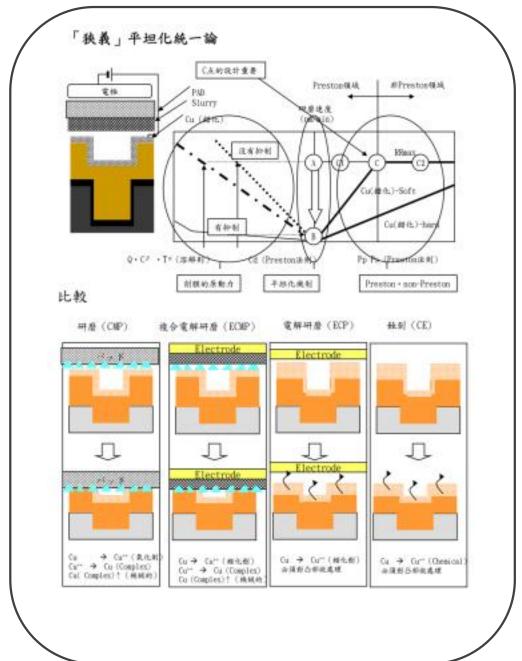

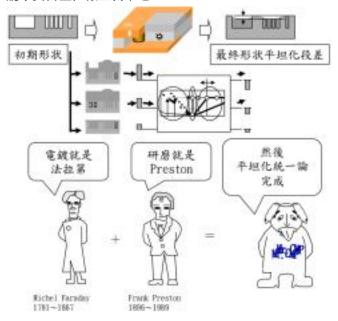

### 平坦化統一論

本節介紹45nm世代以後的最先進鑲嵌配線平坦化技術。內容有僅包含研磨(削膜)技術的「狹義」平坦化統一論,以及包含電鍍(成膜)技術的「廣義」平坦化統一論。如此一來,最後產生的技術就是mC2製程。是不是覺得話題也太壯大了? 我借用了愛因斯坦知名的相對論,稍微起了玩心,還請見諒。那麼我們就開始來談談很受學生歡迎的鑲嵌技術平坦化統一論吧。

#### 平坦化技術百家爭鳴

1980年代後半,研磨技術以平坦化革命技術之姿登場。剛開始是應用在層間絕緣膜的二氧化矽膜 (SiO<sub>2</sub>) 平坦化用途上,之後不僅應用在STI (Shallow Trench Isolation)、鎢通孔、鋁鑲嵌、銅鑲嵌等用途,且用途還持續增加,最近甚至開始研究應用在研磨金屬閘極的可能性。另外,研磨的型態本身也持續進化。特別是層間絕緣膜從二氧化矽膜 (SiO<sub>2</sub>) 改為以低介電常數為目的的低強度Low-k材料後,以降低研磨壓力為目的的各種技術開始展現在世人面前。其中除了一般的研磨CMP

(Chemical Mechanical Polisher)以外,還有應用電解的複合電解研磨ECMP (Electro-Chemical Mechanical Polisher)、同為電解研磨ECP (Electro-Chemical Polisher),以及運用蝕刻CE (Chemical Etching)的方式,還有結合以上技術的複合技術等。

最近因為平坦化技術一次突然冒出太多種,讓人不禁想問「哪個技術才是主流」。 而且,由於在電解應用的領域中,專業用語尚未統一,現在甚至會有人問我:「電解研磨不用研磨粒嗎?」確實,在日文各項報導或論文中,的確可以發現電解研磨(不用研磨粒)、複合電解研磨(會用研磨粒),以及ECP與ECMP等混在一起使用的現象。作者就寫錯了,讀者讀到昏頭也是理所當然的事吧。

接下來我將試著先說明低壓研磨需求的背景與目的,在介紹各種低壓研磨的同時,將所有的平坦化技術統一成一個理論說明。本節的標題「平坦化統一論」不是真的在講理論,而是透過釐清掌管各種技術的平坦化原理,以淺顯易懂的方式統一整理各種技術。而事實上,我的學生都很喜歡這個統一理論(?)。也希望這個整理能成為已經搞混的讀者用來協助釐清的好教材。

### 低、再低、要那麼低?

••••••

#### 為什麼現在要談低壓化?

正如各位讀者所知,為了降低半導體RC延遲的現象,配線的R(電阻)已經以銅取代了鋁。為了降低絕緣膜的C(寄生電容),目前已經提出了許多低介電常數的候選材料。若介電常數下降,絕緣膜的強度與硬度也幾乎會等比跟著下降。再考慮到與基底膜的密著性,過去便一直提倡採用低壓研磨來解決這些問題。右圖為晶片的變遷與採用Cu/Low-k的鑲嵌構造例。Low-k材料基本上是使用電漿處理的二氧化矽膜(SiO<sub>2</sub>)、導入氟(F)的SiOF膜、以甲基(-CH<sub>3</sub>)等置換的SiCHO膜,以及上述材質的多孔膜等。圖中的配線與通孔Low-k材質雖然不同,但也有些例子是採用相同材質的。另外也有無需使用ES(Etch Stopper)的情況。而DCL(Dielectric Cap Layer)採用Si-N、Si-C、Si-CN等材質。

#### 多低的低壓?

那低壓要求要多低? 先來看看Low-k的物理特性吧。圖中所示為介電常數與楊氏模數的相關性。SiO2的強度約為70GPa。SiOF膜也有約40GPa的程度。但Low-k材料的材料強度幾乎都在IOGPa以下。當然,會賦予膜壓的晶片製程不是只有研磨。大家也都知道熱循環或封裝時接合的膜壓反而還比較高。但是膜壓並不是出現一次壓力就會破壞(這個不需討論),而是類似慢慢累積的疲勞。所以在所有製程中所賦予的壓力當然是越小越好,而研磨也因此有了低壓化的需求。

當然Low-k材料也並非維持這樣就好,目前已經有人在開發強度高的Low-K材料 (IOGPa以上)。甚至也有人進一步開發透過UV或電子射線提高約5GPa的材料的強度的製程。

顯示強度的楊氏模數是Cu/Low-k鑲嵌構造的降伏或破壞強度的大概標準。硬度這個研磨的宿敵雖然是傷痕的判斷標準,但一般來說楊氏模數低的材料硬度也低。另外,剝落也是研磨問題之一,故密著性也很重要。一般來說密著性是參照四點彎曲法的測定值,其範圍多在5~10J/m²,但最好是能在IOJ/m²以上。而目前也已經有人發表了提升密著性的製程開發。

## 微細化與整合鑲嵌構造(damascene)的變遷 Cu/Low-k damascene構造 微細化 200 mm 350 nm 45 nm 200 may Cu device Barrier Low-k (ULK) SiO<sub>2</sub> → SiOF → SiOC →Organic → Porous 80 (GPa) PE-SiO 60 Modulus 50 SiOF 30 S SiOC Young' MSQ/PAE Dielectric Constant : k 介電常數與楊氏模數的相關性

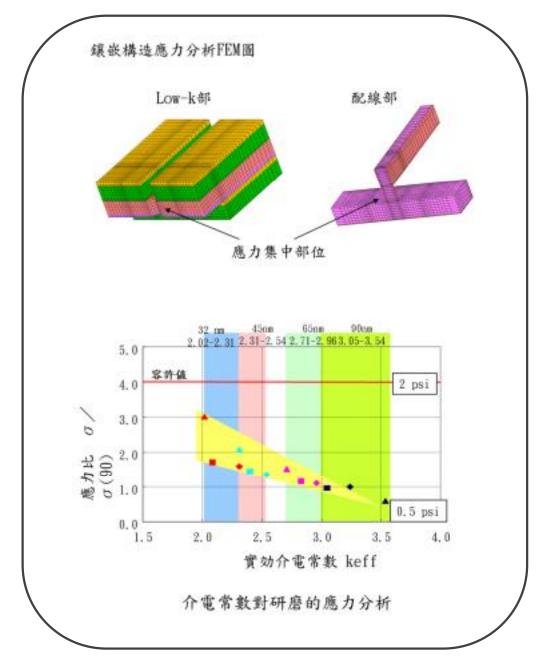

### 那就以分析進行實證

又到了有限元素法活躍的時候了。施以多少壓力後,鑲嵌構造會怎麼改變呢? 若要進行分析,除了這裡介紹的應力分析法之外,要調查像低介電常數的材料就必須應用到破壞力學。雖然也可以直接使用應力場的分析,但差別在於採用應力或破壞能量作為判斷基準的不同。

#### 應力分析

關於這些強度與密著性的分析,有限元素法非常有用。

首先讓我們先看到鑲嵌部位的分析圖。分析分為配線部分與低介電常數部分進行。 不論哪一個部分,結果都是通孔根部的應力最高。

#### 分析結果

這裡的例子採ITRS (International Technology Roadmap for Semiconductors) 日後預測的鑲嵌構造,說明該應力分析的結果。横軸是依據預估各種Low-k介電常數所計算出的實效介電常數,縦軸是Cu配線或Low-k材料內部的應力比 $\sigma/\sigma$  (90)。 $\sigma$  (90)是90nm世代鑲嵌構造以0.5PSI進行研磨時的應力, $\sigma/\sigma$  (90)是將各世代鑲嵌構造的應力以比例的方式呈現。圖中也將90nm世代以2PSI研磨時的應力値作為容許值,以供參考。銅配線部分與Low-k部分因為都在通孔根部附近而成為最大應力,該應力值即為 $\sigma$ 。這是推估各世代鑲嵌構造研磨壓力很有用的資料。

就像這樣,由於Low-k的強度會變弱,可能因研磨而剝落、歪斜或刮傷,因此才會有低壓的需求。然而,若以低壓研磨,當然會導致研磨速度降低而CoC (耗材成本)升高,因此應該還是要有個適當 (可妥協的)數字才對。

在此也描述一下破壞力學應用的結果以供參考。在破壞力學中,雖然低介電常數材的強度是個問題,但被上下夾住的異種材料的matching的問題反倒比較大。只要這個matching沒有過度極端的錯誤,結果將與本分析的結果相同。

### 各種加工方法

過去的平坦化技術

首先為各位介紹過去各種平坦化技術。

① 磨削 (Grinding)

雖然運用於磨削晶圓背面,但沒人用在半導體晶片面。會有Defect很多的缺點。

② 固定研磨粒 (Fixed Abrasive或Bonded Abrasive)

原理介於磨削與研磨之間。固定的研磨粒變為游離,削膜原理與游離研磨粒──也就是研磨的原理相同。平坦化性能佳,故獲部分STI製程採用,但有必須降低Defect的課題。

③ 研磨 (CMP)

Cu研磨的進行順序為(I)以氧化劑氧化Cu、(2)以錯化劑產生Cu的錯合物、(3)以機械性方法去除Cu錯合物。

接著,低壓化需求終於出現,下一世代的技術因而開發。

#### 電解應用、蝕刻應用與複合技術

④複合電解研磨 (ECMP)

Cu的複合電解研磨進行順序為(I)以電能與部分氧化劑使Cu氧化、(2)以錯化劑產生Cu 錯合物、(3)以機械性方法除去Cu錯合物。

也就是說,除了(I)的氧化方法之外,其他步驟都與研磨相同。所以平坦化性能也與研磨相近。但仍有許多如兼顧電解設計與平坦化設計的研磨墊開發問題。

⑤ 電解研磨 (ECP)

與電鍍相反,有時相對於Plating被稱為Di-Plating。從電解集中處開始進行研磨(蝕刻)即可平滑化。但因為電解集中只限於某些圖案,故無法達到如研磨的平坦化降低性能。話雖如此,但我對ECP的期望依然很大,日後可望演變出許多革命性技術。例如目前有人正在開發在超純水中,只針對離子交換體接觸部位進行削膜處理的特殊電解研磨。

⑥ 蝕刻 (CE)

在乾式製程中,等方性與異方性蝕刻雖然已經是常識了,但此技術是試圖以濕式蝕刻達到異方性蝕刻的的技術。MEMS雖然也有採用濕式,但材料有所限制。在半導體晶片上的應用仍有諸多問題。

### 各種平坦化技術比較

| 製程     | 平坦化長度 (mm | ) 加工壓力 (PSI) | 加工面程度 |

|--------|-----------|--------------|-------|

| 研剤     | > 2 0     | 大            | 大     |

| 固定研磨粒  | ~20       | ф            | ф     |

| 研磨     | ~2        | 0.25~10      | 9     |

| 複合電解研磨 | ~2        | 0 · 25~10    | 少~中   |

| 電解研磨   | ~2        | 0            | 少~中   |

| 6k5]   | 0 (~?)    | 0            | 少~中   |

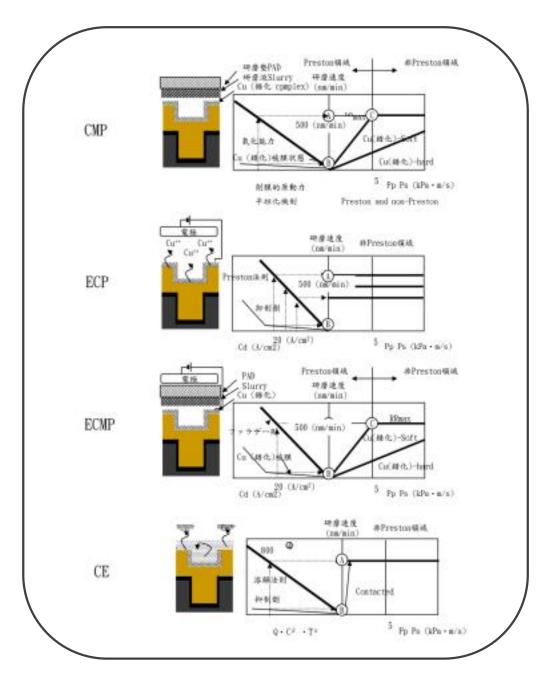

### CMP / ECMP / ECP / CE: 這是什麼?

#### (狹義) 平坦化統一論

Cu研磨的低壓研磨中有CMP、ECMP、ECP、CE與其複合技術。右圖所示為其概要與原理。 以下將針對其原理介紹各技術的特徵。

#### CMP原理 (Preston法則)

我們先看圖。圖的横軸左側是削膜的原動力與平坦化的機制,横軸右側是CMP中常見的壓力  $P_{\rm p}$  (kPa) 與相對速度的 $P_{\rm s}$  (m/s) 的乘積。而縦軸則是研磨速度 (nm/min)。 A點為削膜原動力之例,B點為原動力被抑制的狀態之例,若為CMP製程,首先以氧化劑使Cu氧化為Cu++ (A點)。 再以錯化劑使Cu++變成Cu(錯合物) (B點)。

再以機械性方式將此Cu(錯合物)去除,該速度與研磨壓力  $(P_p)$  與相對速度  $(P_s)$  成正比。以上雖然遵守Preston的算式,但研磨速度會因為Cu(錯合物)的種類不同而產生變化。

#### ECP (法拉第法則)

横軸左側是電流密度 $C_d$ (A/cm²),削膜原動力遵守法拉第法則,與電鍍成膜相反。另抑制效果以添加劑來進行。平坦化的機制裡,除包含選擇性磨除電解集中等突出部位的傳統電解研磨原理之外,實務上還必須進行更進一步的處理。

#### ECMP原理(法拉第法則與Preston法則)

横軸左側是電流密度 $C_d$ ( $A/cm^2$ ),削膜原動力與ECP相同,都遵守法拉第法則。先以電能使Cu氧化為Cu++(A點),其後的過程與CMP完全相同。以錯化劑將Cu++處理成Cu(錯合物)後(B點),再以機械性方法去除此Cu(錯合物)。前段製程的氧化屬於法拉第法則,磨削速度則屬於Preston法則的領域。也就是說,只有氧化製程不同,其後都與CMP相同,故平坦化機制可說是與CMP相同。

#### CE (溶解法則)

横軸左側為蝕刻劑流量 (Q)、濃度 (C)、溫度 (T) 的乘積  $Q \cdot C^{\alpha} \cdot T^{\alpha}$ ,削膜原動力遵守溶解法則。抑制效果採用添加劑進行。因蝕刻液會進行全面溶解,故基本上並無平坦化能力。選擇性溶解凸出部位的處理是以添加劑等進行。

### 「狹義」平坦化統一論

#### 「狹義」平坦化統一論

圖為各種技術及其適用法則之統一整理。

首先,CMP適用研磨速度與下壓壓力及相對速度成正比的Preston's Law; ECP 適用研磨速度(量)與電量成正比的Faraday's Law; CE適用研磨(溶解)速度與流量、濃度、溫度成正比的融解法則。橫軸左邊為削膜的削膜原動力。例如,CMP的 話就是氧化劑的氧化力(從Cu變成Cu++),ECMP或ECP的話就是電能的氧化力,CE 的話就是溶解力。為了方便比較研磨,橫軸右邊是Preston算式的參數——研磨壓力  $(P_p)$  與相對速度  $(P_s)$ ,縱軸為研磨速度。此縱軸所標示的A、B兩點之研磨率之差,代表的是平坦化性能。

#### 與說明圖之比較

請讀者比較上一節的說明圖,應該可以更加理解。

像這樣理解各種基本技術之後,應該也就會知道怎麼應用。現在市場上正在使用的Cu平坦化技術,就是這些技術的應用。希望讀者能好好思考一番。一般領域的Cu加工技術原本是蝕刻與電解研磨,半導體中採用的研磨反而算是異類技術。因此蝕刻與電解應用會應用在Cu加工技術上也是理所當然的。只是應用時還要在半導體晶片平坦化上多下點工夫就是了。而研磨已經在平坦化上下過功夫,是個已經成熟的技術。這是在一般領域已經成熟的蝕刻與電解研磨技術,以及在半導體領域已經成熟的研磨技術的競爭。但我覺得它們之間若有合作應該也不錯。

另外,研磨後的表面狀態跟下一個製程的洗淨結果有很大的關係,而洗淨後的表面狀態又對再下一個製程的乾燥結果有很大的影響這點,自是不用再多說的了。

接下來讓我們進入包含成膜在内的「廣義」平坦化統一論。

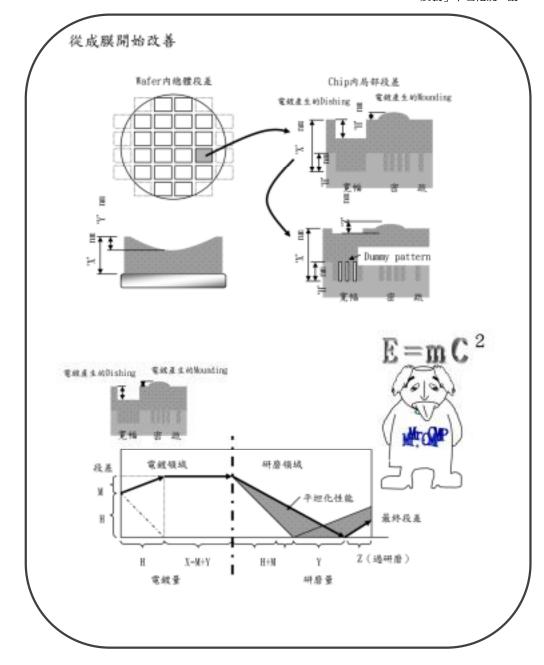

### 「廣義」平坦化統一論

#### 包含成膜技術在内的「廣義」平坦化統一論

首先先來解釋總體 (Global) 段差與局部 (Local) 段差。如右圖所示,以電鍍形成銅膜時,會產生晶圓高低不均的現象,這個現象稱為電鍍總體段差。而晶片層高低會因為配線的疏密而產生高低差,這個就稱為電鍍的局部段差。電鍍的總體段差因電鍍技術的提升,目前已經達電鍍量約5%(3σ)的程度。在局部段差中,電鍍的Dishing就等於配線高度,因此無法就由電鍍技術解決,目前是依靠假鍍圖案等晶片設計來改善。電鍍的Mounding則嘗試藉由結合晶片設計與電鍍液設計來解決。

讓我們重新檢視一次從成膜到削膜的平坦化方法吧。在一般的電鍍當中,電鍍的 Dishing大小會受到假鍍圖案有無與否的影響。如果可以進行平坦化電鍍的話,初期 高低差可以做到極小。總體段差加上局部段差的總高低差就是下一個削膜製程需要進行平坦化處理的初期段差。如果這個量很大,且下一個製程的削膜技術平坦化性能又差,為了有足夠的空間進行平坦化,成膜量也就必須多一點才行。當然,如此一來CoC 也就差了。

考量這個成膜製程的初期段差與削膜技術的平坦化性能並決定最佳的成膜量與 削膜量,即是(廣義化的)平坦化統一論。實務上也就能輸入成膜製程數據與削膜數 據到電腦裡面,即獲得最小CoC的最佳製程。

相對於只有削膜的「狹義」平坦化技術統一論,筆者將從成膜到削膜的這個一連 串系統稱為「廣義」平坦化技術統一論。如上所述(也不用多說),這個統一論不是 學術性學說,但應該可以幫助了解鑲嵌製程的平坦化,也很受學生歡迎。希望可供讀者參考。

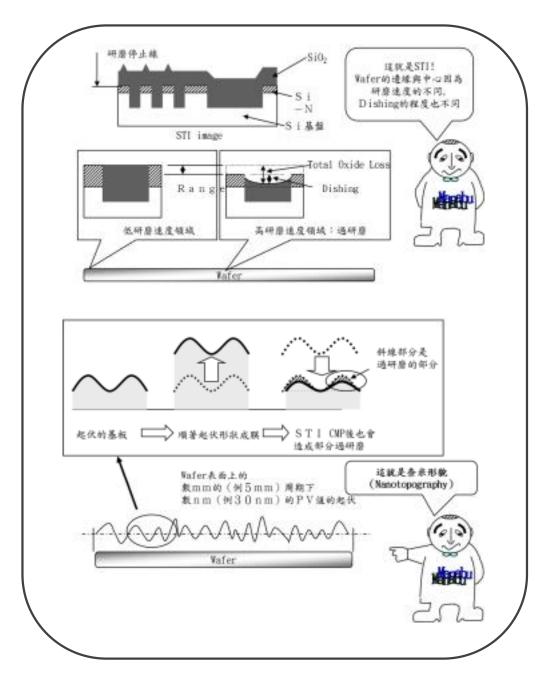

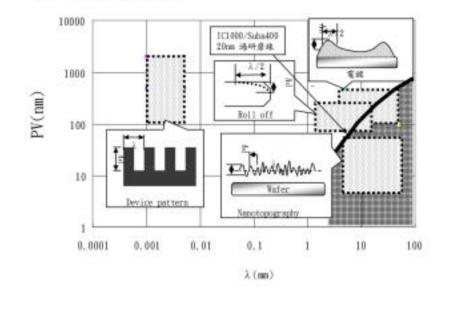

## 奈米形貌(Nanotopography):STI良率惡化!

#### STI的良率?

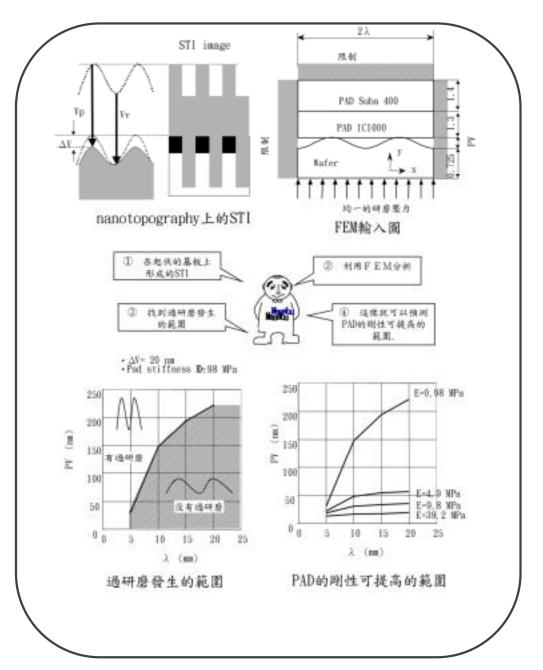

在STI用CMP領域中開始傳出了怪事。那就是最近晶圓的起伏(waviness)會給CMP後的良率帶來不好的影響。CMP本來就是沿著大起伏而非小起伏進行平坦化的製程。而這起伏大小可透過研磨墊與研磨液或CMP運轉條件來控制,且這個方法在半導體晶片平坦化製程中已經獲得成功。但是隨著CMP平坦化性能的提升,又會出現晶圓的起伏形狀、大小對STI製程帶來負面影響的可能性。大眾都已經很了解透過FEM的段差特性分析,這裡我將依CMP種類將晶片膜構造分成四大類別,以FEM分析STI的CMP特性,並更進一步分析晶圓起伏對STI的影響。

#### 晶圓起伏的影響

如圖所示,目前晶圓以數mm到數十mm的周期(λ)呈現數十nm高度(PV值)的起伏。最近的報告指出,這種起伏會對STI的CMP處理時的良率造成影響,並在奈米形貌(Nanotopography)上引起討論。此後這種起伏即定義為奈米形貌。如圖所示,STI是先沿著奈米形貌形成氧化膜,之後再沿著成膜表面的凹凸進行CMP研磨,但這其中包含沿著成膜表面研磨,以及不沿著表面而對突出部分進行過研磨加工的兩種情況。像這種初期晶圓的奈米形貌在經過成膜製程與STI製程後,會對CMP造成什麼影響?又該如何避免影響呢?以下我將介紹分析例子。

### 竟然不沿著起伏研磨!

.....

#### 分析晶圓起伏的影響

分析圖如右圖。成膜後對谷底部位研磨的研磨量為V, 突起部位的研磨量V,與谷底部位的研磨量V之差為 $\Delta V$ 。將 $\Delta V$ 低於某個容許值的條件,定義為*奈米*形貌不會對 STI的CMP製程帶來不良影響的條件。終止層與STI膜之間的研磨液選擇比若為1,則 STI的過研磨量僅為 $\Delta V$ 。

$\Delta V = (V_p - V_v) < V_{al}$  at  $V_v$

其中, ΔV: 谷底與頂端的研磨量差 (過研磨量)

V<sub>2</sub>: 頂端研磨量V<sub>3</sub>: 容許過研磨量

#### 分析結果與對策

右圖為奈米形貌特性值的周期 $\lambda$ 、高度PV與晶片過研磨量 $\Delta V$ 的關係(研磨墊為 IC1000 + Suba400, $\Delta V$  = 20nm)。圖的左上方由於PV大、 $\lambda$ 小,為會發生20nm以上過研磨的區域。而右下方則為相反的PV小、 $\lambda$ 大,為不會發生20nm以上過研磨的區域。另外圖中也呈現出改變研磨墊剛性時的情況。剛性若大,則容許區域會變小,這代表就奈米形貌而言,若使用像Suba等剛性小的研磨墊,則容許區域就會變大,反之若使用IC1000單層等剛性高的研磨墊,則容許區域就會變小。

#### 對策

接下來將闡述CMP製程的補救措施。若使選擇比大於I,則因晶圓起伏所造成的過研磨會與選擇比成反比例降低。但由於若研磨液的選擇比變大,一般來說會也會使Dishing跟著變大,故不能輕率提高選擇比。一般選擇比可調整範圍約30左右。必須依據所使用的晶圓的奈米形貌容許值、半導體晶片設計的終止層膜厚內範圍與Dishing容許值來決定適當的CMP製程。

特殊開發例 Roll-Off: 邊緣垂下

### Roll-Off: 邊緣垂下

•••••

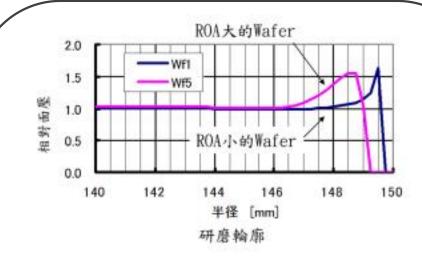

#### 什麼是Roll-off問題?

晶圓外緣倒角部位附近比晶圓中央的平坦度差,這個比晶圓的平坦面還要稍微下垂的部位即為Edge Roll-Off (ERO)。在雙面研磨的300mm晶圓中,這ERO的範圍已知甚至到達ITRS2003年版規定為2mm的Edge Exclusion (E.E.) 的內側 (Fixed Quality Area: FQA)。因為這個原因,在光刻製程中,晶圓邊緣部位無法滿足最先進晶片所要求的平坦度,因而成為問題。

而這個ERO在CMP製程中是否該視為是個問題,本身就是個很有趣的問題。在此 我們就使用有限元素法(Finite Element Method: FEM)來分析ERO對CMP研磨輪 廓造成的影響。

#### 分析方法

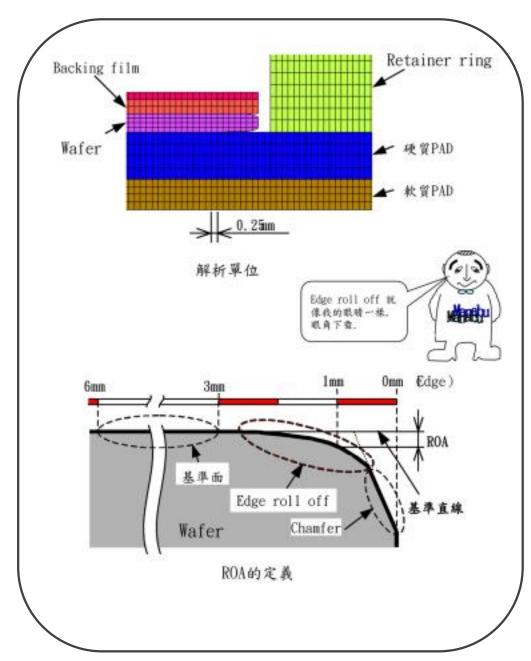

假設CMP的研磨率可以用Preston的算式表示,為了預測有ERO的晶圓的研磨輪廓,使用FEM分析計算面壓分布。分析中忽略晶圓與研磨墊的旋轉,僅考慮垂直方向的壓力。又以晶圓中心為對稱軸的二次元圓筒座標進行分析。

晶圓邊緣周邊的分析網格如圖所示。晶圓為φ300mm、厚度0.775mm,倒角形 狀為梯形。研磨墊的基層為軟質研磨墊、表層為硬質研磨墊的積層構造。晶圓背面透 過Packing film施以等分布壓力(晶圓壓力)。

晶圓的周圍採用固定環(Retainer Ring: R.R.)施以壓力。

### 以邊緣1mm為目標

### Edge Roll-off 的影響

晶圓壓力與固定環 (R.R.) 壓力若皆為30kPa時,晶圓邊緣部的面壓分布將如圖所示。此處縦軸是以晶圓中央部位的面壓為I時的相對面壓,如前所述,其可大略視為與研磨輪廓以及傾向一致。在ROA (Roll Off Amount) 小的晶圓中,已知在半徑148mm以內的相對面壓幾乎為一樣而ROA大的晶圓則是當半徑大於146mm時相對面壓會越來越大,已知在半徑148mm處的相對面壓比在晶圓中央部位大約30%。

又假設當E.E.為2mm時的FQA的研磨量變動容許範圍為±10%,意即當相對面壓設定為1.0±0.1,ROA小的晶圓的相對面壓就會進入容許範圍內,但ROA大的晶圓的相對面壓將遠超過容許範圍。故ERO對晶圓邊緣部的研磨輪廓的影響很大,有可能會對CMP製程造成問題。

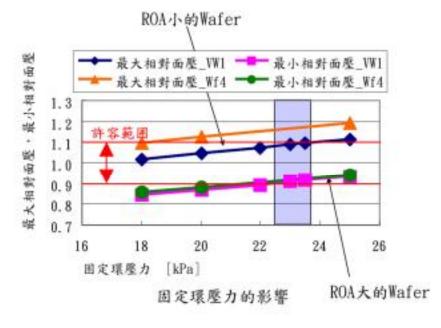

#### 固定環壓力的影響

右圖為E.E.為2mm時,針對不同晶圓調查FQA的最大相對面壓、最小相對面壓與 R.R.壓力的關係的結果。此處晶圓壓力固定為30kPa。

在這R.R.壓力範圍中,最大相對面壓與最小相對面壓會隨R.R.壓力變大而變大。 在此,可以發現在ROA小的晶圓中,R.R.壓力為22.3kPa到23.8kPa的範圍間(有顏色 部位),位於相對面壓的容許範圍內。而另一方面,在ROA大的晶圓中,最大相對面 壓與最小相對面壓的差值大,R.R.壓力皆不在容許範圍內。

由這個結果可知若ROA小,則可調整R.R.壓力來解決ROA的問題。但如果ROA太大,則不管怎麼調整R.R.壓力都會超過容許範圍。

以上以FEM分析探討了晶圓Edge Roll-Off對CMP研磨輪廓的影響。其結果是 Edge Roll-Off對晶圓邊緣部位的研磨輪廓影響很大。當ROA為1.27時,在半徑 148mm處的相對壓力比晶圓中央較大約30%。但CMP製程中可容許Edge Roll-Off 的幅度有限,若ROA小且變動小,則可透過調整固定環壓力來解決問題。

### FEM, 從公里到奈米

•••••

#### 可適用於奈米等級的構造分析

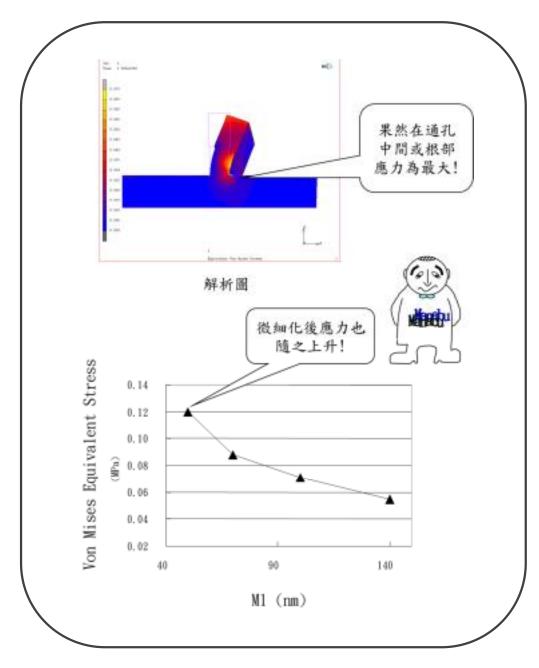

隨著LSI的高集積化與高速化,大家也開始研究使用比傳統SiO2介電常數更低的材料(Low-k材料)。作為Low-k材料,內部有許多孔洞(介電常數I)的多孔材質與有機材料是很有發展可能的材質,但這些材料的機械性強度低,可能會成為製造製程上元件受損的原因,進而導致良率與可靠性降低。在半導體製程中,會有熱或加工反作用力等施加在配線構造上的各種負荷。在此我預測未來可能獲採用的材料機械特性,並以有限元素法分析進行CMP時會作用在配線構造上的應力。

#### 分析條件

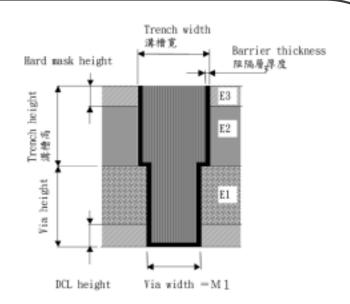

以下針對以雙鑲嵌法形成之配線構造,假設未來絕緣材料的機械特性、配線尺寸 與構造後,以有限元素法分析CMP平坦化製程中所產生的應力。

- (I) 配線構造與尺寸: 圖為via與其上層配線的模式圖。表中的假設尺寸以via直徑的單位表示(單位為nm)。另針對以下三種構造進行分析: ①E1、E2、E3均一材料的Homogeneous without HM構造、②僅E3不同的Homogeneous with HM構造、③El~E3皆不同的Hybrid with HM構造。

- (2) 材料機械特性: El~E3的材料是依據ITRS等各Technology node (T.N.) 的bulk比介電常數來決定Low-k材料的楊氏模數預測值。此外,配線材料 (Cu)、阻隔層 (Ta/TaN)、擴散防止膜 (SiCN) 不隨尺寸改變並呈一定值。

- (3)分析網格與負重條件:分析模型是圖中的配線(最小幅度)與via,再加上在下層模擬最大幅度的配線、相當於一層半的三次元模型。MI=100nm時,模型整體為µm× lµm× 0.6µm。並以Via中心為對稱軸,限制分析模型的最下層。分析網格的兩端採用模擬無限遠的半無限元素。CMP時的負荷負重則假設為在整體分析模型上面平均施以3.45kPa (0.5psi)的垂直負重以及摩擦係數0.43的截斷應力。

Damascene構造圖

### FEM分析輸入数值 (nm)

| M1        |            | 140    | 100 | 70  | 50   |

|-----------|------------|--------|-----|-----|------|

| Trench    | Width (mir | ) 160  | 114 | 80  | 57   |

|           | Width (max | ) 1000 | 500 | 300 | 100  |

|           | Height     | 230    | 170 | 125 | 90   |

| Via       | Width      | 140    | 100 | 70  | 50   |

|           | Height     | 210    | 150 | 110 | 80   |

| Hard mask | Height     | 50     | 35  | 25  | 25   |

| DCL       | Height     | 50     | 35  | 25  | 20   |

| Ta/TaN    | Thickness  | 10     | 7   | 5   | 3, 5 |

### 來確認鑲嵌強度吧

•••••

#### 根部應力最大?

圖為從配線構造部通孔中心的對稱軸面來看的von Mises等效應力分布,以及此時變形狀態的例子。通孔底部是由擴散防止膜(SiCN)支撐,應力在通孔中間或根部為最大。這結果想像一下應該不難理解。

另外,下圖為此通孔部的應力以微細化後的尺寸MI為參數畫成的圖表。透過此圖可了解每個世代應力上升多少。

#### 那對策呢?

預測隨著LSI高性能化之Low-k材料演變,並分析CMP作用在配線構造的應力。 通孔部的應力雖然有隨著Low-k材料的楊氏模數變化的傾向,但因變化率不大,既使 是相當於32nm世代(2010年)的情況,應該也還不會嚴重到需要擔心的地步。這表 示,就通孔部的應力而言,無須極度降低CMP時的加工壓力。

此處又從變形與降伏的角度探討了von Mises等效應力。以結果來說,我們可以發現,FEM從機械工學「公里」等級到半導體「奈米」等級的分析都派得上用場。學機械的到處都有,希望讀者能充分活用。

最後,我要來回答「Low-k是脆弱的材料,只作應力分析不夠吧?」這個問題。 沒錯。就剝離或剪截斷等情況來說,要討論作用在配線構造上的應力,就必須做包含 破壞應力的分析。但是用於該分析的應力與此處分析的應力是相同的。也就是說,應 力已經用FEM分析過了。就只看是要當作容許應力來做判斷,還是當作破壞應力,重 新計算能量後再做判斷。所以破壞應力也是可以用這種方式分析的。

#### Who's Law?

半導體在過去60年反覆透過微細化與大口徑化為世界帶來繁榮。那麼引領半導體技術的人是誰呢?

說到微細化,便以Intel戈登. 摩爾博士的摩爾定律(經驗法則)最為知名,但其實支撐這個理論的是IBM的羅伯特. 海思. 丹納德博士的CMOS相似法則。摩爾博士以自家公司的晶片生產技術為基礎,根據「經驗」預測了「半導體集積密度每18~24個月會增加一倍」。丹納德博士則發表論文並以「學術方法」驗證了CMOS晶片細微化後,將會①高速化、②低耗電化、③低成本化。在那之後,半導體一直走在微細化這條路上,引領其發展的技術就是DRAM記憶體。而在記憶體領域中,「促進每年微細化進展」的黃氏定律(三星的自家公司計畫)也是挺有名的。

那晶圓大口徑化有定律嗎?當8时晶圓廠有300間時,晶圓技術就步入12吋了,所以當12吋晶圓廠也同樣有了300間時,也許就會步入18吋時代了吧。這是誰的定律?

未來也會持續出現像3D堆疊封裝與Emerging Research *Device*等半導體典範帶來的大轉型。 這些又會是誰來帶頭引領呢?

Who's Law? 世界正在等待英雄的出現。

144

# 第四篇

# Wet Surface Treatment Process: Cleaning and Drying

濕式表面改質製程: 洗淨與乾燥

半導體製程的洗淨

## 洗淨是戰場

#### 什麼是半導體晶片的洗淨?

為什麼洗衣與打掃最辛苦?你洗衣時是否曾經把會掉色的衣服一起丟到洗衣機? 打掃時是否曾經有帶著「髒腳」的小孩幫你打掃?這些在洗淨技術上都定義為 「Contamination (污染)」。

半導體晶圓的洗淨面混有許多材料。在我們為了看得到銅配線而擦拭表面時,目的是要擦掉旁邊氧化膜上的銅,但是抹布會不會經過銅配線呢?這就像是想擦乾淨墨斗旁邊,卻又毫不在意地不停劃過墨斗上方,怎麼可能擦得乾淨?!

先來學習打掃的基礎吧。

為了解決以上問題,最近有人正在開發非接觸式洗淨與軟式洗淨的技術。非接觸式洗淨是指不接觸墨斗,軟式則是以不會傷害到銅的方式洗淨。還有乾燥也很費工夫。乾燥後不留下水痕的乾燥方法很重要。也就是不留下痕跡的軟式作法吧。

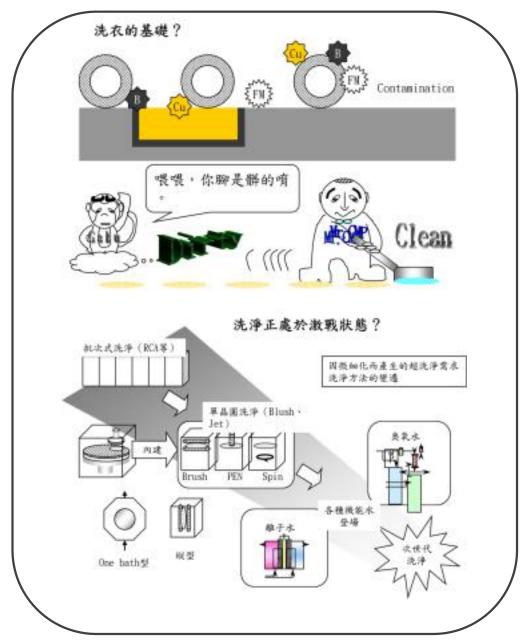

#### 洗淨歴史的概要

洗淨歷史的概要如圖所示。傳統是以RCA公司所開發的批次式 (batch type) RCA 洗淨法為主流,但隨著CMP與電鍍等濕式製程裝置出現後,Dry in、Dry out概念普及化的同時,各種裝置內建單晶圓清洗機的方式也逐漸普遍。之後也開發出各種適合單晶圓的洗淨裝置與製程。以設備來說,出現了將所有製程集中在單一洗淨槽 (Bath)裡進行的「One Bath型」,以及將晶圓以縱向進行洗淨的「縱型」等類型。而製程上則出現了使用離子水與臭氧水等各種機能水的製程。在ITRS所指出的新材料與高寬比世代中,洗淨技術的開發將必然成為關鍵技術。

雖然都叫洗淨,但其方式也是千奇百種、天差地別。洗淨業界真可謂是「激戰狀態」啊。

## 要清什麼? 怎麼清才乾淨?

大统以CNAD为例 给职而进行的具体疾运动物质 温方面电体疾病现在进行

本節以CMP為例,說明要洗掉的是什麼污染物質、還有要用什麼原理來洗掉。

#### 要洗什麼?

我先以CMP為例來說明。在經過CMP製程後會有微粒或金屬造成污染,也會因不同製程所選的研磨液(二氧化矽系列、氧化鋁系列、錳系列等)、研磨墊細屑、研磨物等造成汙染。為了不讓研磨時所產生的細微刮傷更加嚴重,必須將表面、背面與旁邊都洗乾淨才行。要洗掉的對象有上述要進行CMP的氧化膜、鎢、配線材料、阻隔膜材料等,而洗淨方法也會隨著污染物質與洗淨標的的組合不同而改變。特別是使用化學方法時,不能只考慮洗淨效果,還得思考會不會對之後的晶片製程造成限制,所以洗淨方法不是CMP廠商可以自己決定的。

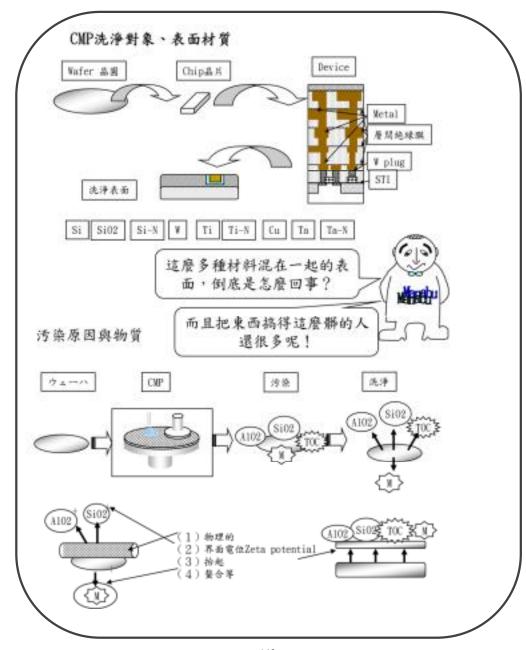

CMP製程上洗淨對象的晶圓表面材質如圖所示。各製程的表面材質不同,應該注意的重點也不同,舉例來說,雖然是銅配線製程,但也不代表表面要洗淨的只有Cu。而是有Si、SiO<sub>2</sub>、Si-N、W、Ti、Ti-N、Cu、Ta、T-N等製程相關材料混在一起。這些都是在考慮界面電位 (zeta potential) 與預防腐蝕時應該要注意的東西。還有電鍍時含在電鍍液内的不純物質——金屬離子與有機物,甚至連從裝置跑出的灰塵都要考慮。

#### 來學習洗淨原理吧

右圖以CMP為例解釋了污染狀況與洗淨原理。因進行CMP所使用的研磨液、研磨墊以及裝置會導致磨粒、金屬、有機物(TOC)等受到污染。考慮到這幾點,洗淨的原理基本上大致可分以下四個項目。

- · 以刷或噴的物理方式將污染物質從表面清除。

- 改變做為媒體的洗淨液 pH 值來控制界面電位,使污染物質因電性而容易脫離洗淨表面。

- · 略將洗淨對象與污染物質一併腐蝕掉。

- · 溶解污染物質或以洗淨液的螯合效果去除。

## 要洗得乾淨就要使用乾淨的裝置

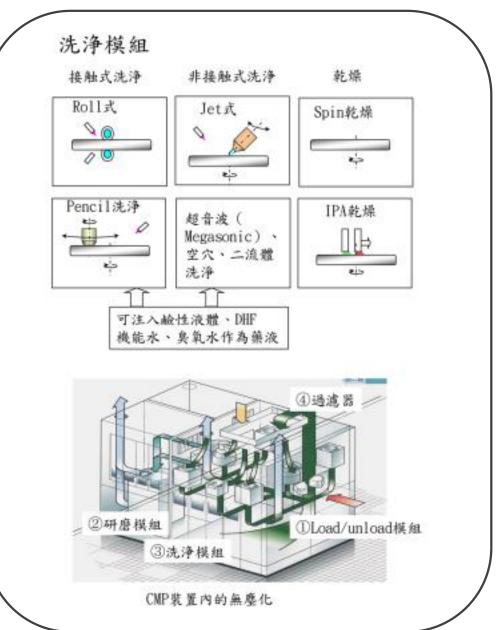

洗淨模組範例如圖所示,以下將描述其特徵。

#### 先講Roll型洗淨

這是單晶圓洗淨機的基礎。這種方式是透過讓PVA等Roll部材以數百轉速旋轉,同時洗淨晶圓的表面與背面。Roll的形狀是各家公司技術的結晶。洗淨時,舉例來說,有的會放入數百ppm的鹼性液體來控制界面電位,有的則放入能使Cu錯合物容易去除的螯合液,液體配方也是相差十萬八千里。因此,我們需要用到酸或鹼性藥液來處理。像這樣放入微量藥液就可以達到提升微粒洗淨效果、延長使用壽命,以及提高除去金屬污染等效果。

#### 再來是Pencil型

基本上Pencil型也是使用跟PVA等Roll相同的部材,以數百轉速旋轉Pencil部位洗淨晶圓表面。 洗淨零件的形狀不是Roll (滾筒)型而是筆型,一般多稱為Pencil型,所以我這裡也沿用這種稱呼。 使用的藥液必須有跟Roll型完全相同的功能。

#### 最後是Jet型

Jet型分為一般Jet型、加上超音波的形式、應用空穴現象的特殊Jet型洗淨。空穴Jet型的可運用範圍比傳統Jet型的範圍更廣,洗淨效率亦更高。現在更有人在開發使用氣體與液體兩種流體的Jet型洗淨技術。此技術同時投入藥液的可行性也不低。

#### 乾燥

在單晶圓式乾燥中,以數千轉進行最終乾燥的Spin dry (SRD) 式是最普遍的。就氧化膜等 親水性膜表面上來說,包含吞吐量,該方式的裝置在許多能力上皆十分優異。目前也有人正在開 發在低介電常數材等材料的疏水膜表面使用IPA (Isopropyl Alcohol) 的乾燥方法,以防止水痕 產生。只要依膜的表面不同使用不同方式即可。

接著,這些洗淨與乾燥模組因為Dry in Dry out概念的出現 而整合到管理確實的裝置內部, 以此達到最佳的洗淨與乾燥效果。

## 讓環境更乾淨吧

#### 環境淨化 (應對新材料)

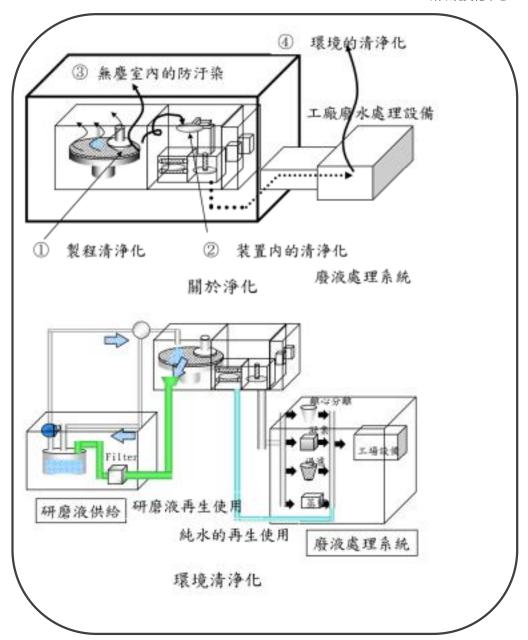

再來談無塵室之外,也就是環境污染對策。半導體晶片逐漸採用許多新材料。配線也從鋁改為銅,且之後銅應該又會演變為銅合金吧。層間絕緣膜的各種無機、有機低介電常數材料的開發也已經進入佳境。而電容器方面,所謂的Ta2O5、STO、BST等高介電常數材料與Pt、Ru、Ir等貴金屬也進入候選名單,電晶體閘極則採用HfO2等高介電常數材料等,半導體晶片材料可說是多到令人眼花撩亂的地步。順帶一題,當我想從元素表中找出這些元素,我發現這些元素全都是些無法簡單獲得的元素。而在加工這些元素的過程中,當然會產生混有這些材料或副產物的廢棄物,導致廢水處理也變得複雜。當然這並非只是CMP需要解決的問題,不過CMP本來就是以髒出名的(不是什麼值得說嘴的事),所以從CMP來解決也是好事,畢竟CMP技術在開發之初就已經十分注意環境問題了。

舉例來說,現在不但正在嘗試循環再生使用研磨液,對於廢棄液體也已經實施了 封閉式回收再利用的作法。關於研磨液的循環再生使用,裸砂研磨原本就已經有數次 循環使用研磨液的作法。而半導體晶片的氧化膜或多矽晶研磨等方式,因為不會含有 異種材料這樣的生成物,所以也可以回收再利用。當然回收使用也是有缺點的,因此 要不要採用就看工程師的決定了。CMP除了廢液内含磨粒這點比較特殊以外,其他方 面與一般廢液處理也沒什麼兩樣。因此與傳統廢液處理設備廠同等級,要採用設備也 方便,但要不要採用也是看工程師決定。

日後使用的新材料應該會像上述的演變一樣越來越多,不但研磨液的規格會隨之改變,廢液處理的規格也會改變吧。我認為與其等全部都都做完了才被要求「反正就是想辦法把它給處理掉」,倒不如一開始就採用環保的研磨液,並開發整合廢液處理的CMP製程。

環境污染對策是必要項目,我們應以環保對策來幫CMP抹除「污染之王」這個不名譽的代名詞。

半導體製程的洗淨

## 引頸企盼的非接觸洗淨

#### 為什麼現在要採用非接觸洗淨?

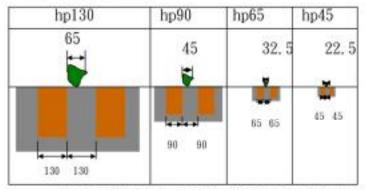

隨著微細化的演進,雜質管理也變得越來越嚴格。以CD (Critical Dimension)的一半來說,45nm世代雜質管理的大小就是22.5mm。這個大小在CMP中來說,不但與平坦化的Dishing幾乎相同,也難以分辨到底是傷痕還是雜質。所以洗淨才從物理洗淨往非接觸洗淨演進。

非接觸洗淨的代表方式為噴水式(Water Jet),除此之外還有噴水加超音波、以水柱噴冰、同時噴射液體與氣體的二流體等方式,這樣看來,我們可知非接觸洗淨的開發也正往許多不同方向進行著。本章將以其中之一為例,介紹應用空穴原理的非接觸洗淨。

空穴噴射 (Cavitation Jet) 跟噴水式一樣,都具有非接觸式、產生超音波、可依目的輕鬆注入機能水、大幅增壓與壓力影響幅度廣等各種特徵。

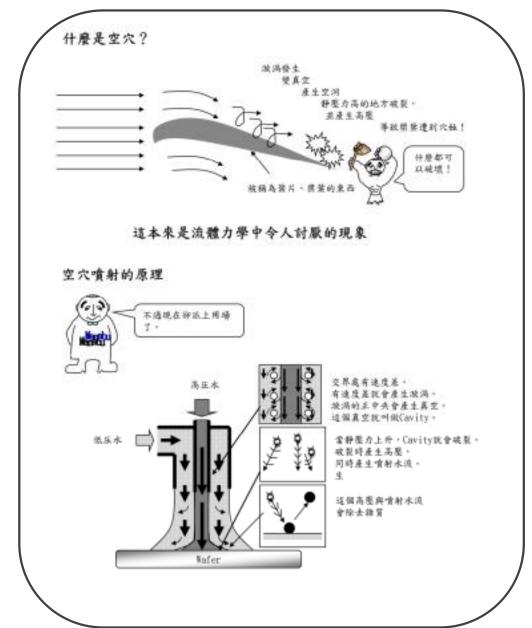

#### 空穴噴射的原理

在流體力學上,本來有種常常要避免的空穴現象,而空穴噴射洗淨就是應用此一物理現象做為洗淨晶圓的方法。在流體中,如果壓力在飽和蒸氣壓以下,就會產生 Cavity (空洞)。壓力又回到飽和蒸氣壓以上時,這個Cavity就會破裂,同時產生極高的瞬間壓力。

實驗裝置範例如圖所示,在低速噴射水流中讓高速噴射水流流過。此時在兩噴射水流的交界處會因為高低速噴射水流速度的差異而產生漩渦,漩渦中心會產生低壓部位,而Cavity就出現在這裡。實驗所假設的洗淨機制,就是這個Cavity在晶圓面破裂時所產生的壓力,具有除去晶圓上微粒的功能。

半導體製程的洗淨

## 馴服野馬

#### 產生空穴現象的情況

若以高速攝影機直接觀察空穴現象,可以觀察到空洞在壓力1~13MPa之間變化時所發生的情況,那簡直就像身處於暴風之中一般。而空穴噴射技術就是試著要馴服這匹本來連岩石也能破壞的野馬。

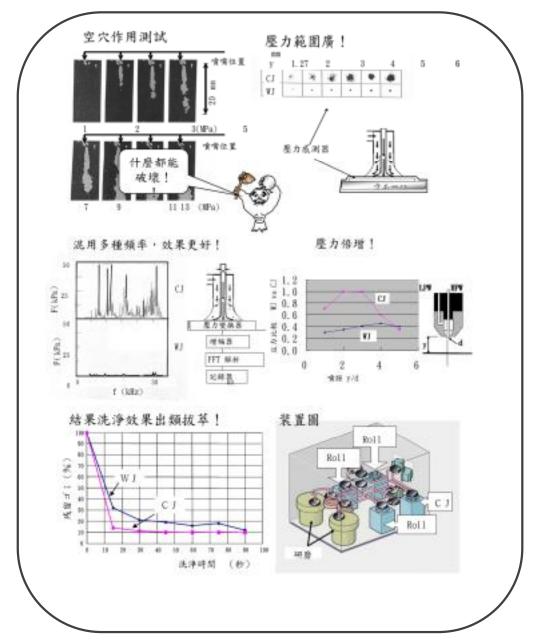

#### 壓力區域廣泛!

若以噴距 (Stand-off distance) 作為變數來比較壓力影響區域,我們可以觀察到空穴噴射比一般噴水式 (Water jet) 的影響區域大數十倍。藉此方法便可縮短單晶圓式裝置洗淨時間。這就像是使用比較大的掃把掃地,當然是越大越快。

#### 混用多種頻率,效果更好!

空穴噴射裡有最高高達60kHz的多種頻率壓力,由此可知,相較於一般的超音波洗淨只使用單一頻率,我們可以運用的頻率範圍更為廣泛。我們應該抱持著不同尺寸的晶圓就會有其適合頻率的想法來思考。

#### 壓力增加數倍!

右圖為以噴距為變數,比較被洗淨面的空穴噴射壓力與Water jet的結果。從圖中可知壓力增幅約達兩倍。在Local可獲得空穴破壞壓力的效果,在Global也可獲得比Water jet高約兩倍的壓力。

這控制壓力的方法有很多技術在其中。要是力道太強的話連石頭也能噴碎吧?

#### 從結果來看,洗淨效果出類拔萃!

關於最終洗淨能力,我們從初期研磨液量設為100%比較殘留%數來看。Water Jet最後殘留量約20%,但空穴噴射則可達10%。若以同樣到達20%的洗淨能力來比較洗淨時間的話。Water Jet 需花費30秒、空穴噴射則只要12秒。以結果來看,不管是最終洗淨能力還是洗淨時間,空穴噴射都勝過Water Jet。

半導體製程的洗淨 難以乾燥的材料就用 IPA

## 難以乾燥的材料就用 IPA

#### 什麼是IPA乾燥?

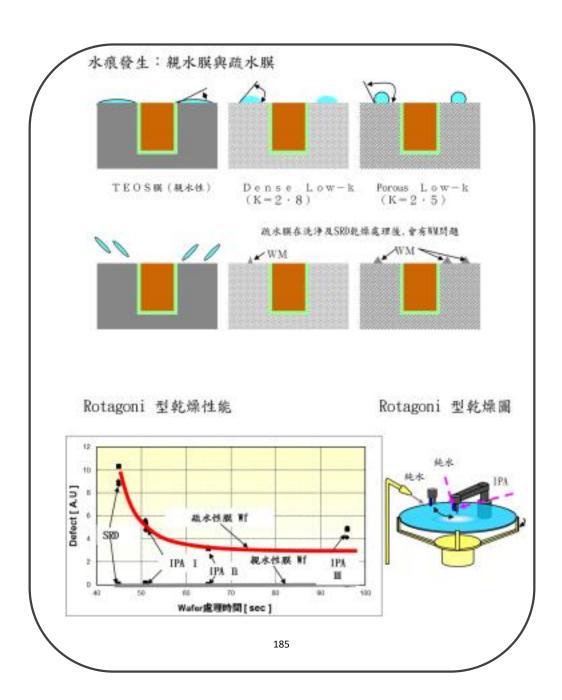

Cu / Low-k配線的CMP製程需要不傷Low-k膜的研磨、洗淨、乾燥技術。疏水性膜的Low-K膜表面容易留下水痕、並對電氣特性造成影響。IPA乾燥技術原本是為前端處理的疏水性膜水痕而開發的技術,但如上所述,最近也開始用在配線製程的疏水性Low-k膜的洗淨與乾燥上。又,雖然IPA乾燥也有應用在親水性膜上的例子,但IPA乾燥是否對親水性膜也有效果則仍需驗證。

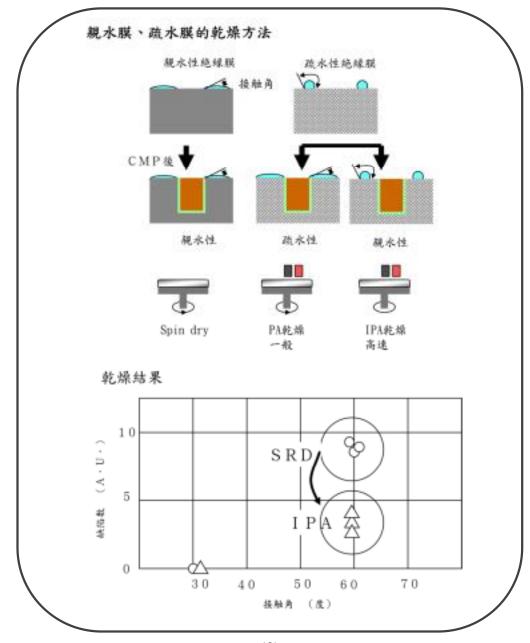

IPA乾燥技術分為以浸漬為基礎的Marangoni型與IMEC開發的正面(Face up)用Rotagoni型。在此提及的是CMP的乾燥技術,因此將介紹Rotagoni型IPA乾燥與一般的Spin rinse dry(SRD)對晶圓表面的親水性膜與疏水性膜的乾燥效果差異。

疏水膜是很難乾燥的材料。要是不解決這個問題,採用低介電常數材料的最新晶片就沒辦法乾燥。真是個大問題。

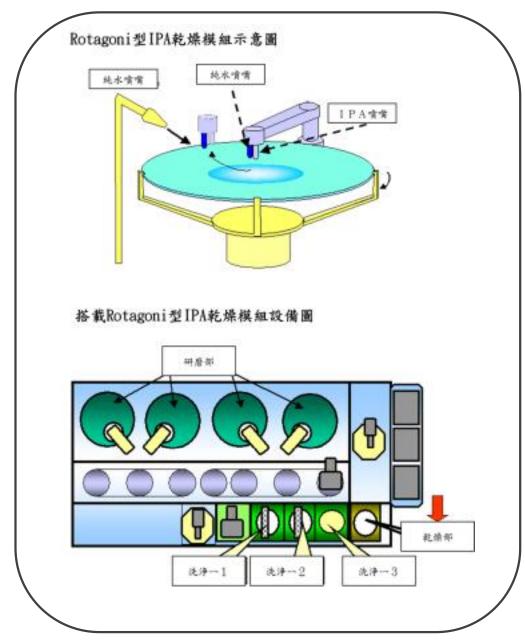

#### Rotagoni乾燥

Rotagoni型IPA乾燥設備的概略圖如圖所示。噴嘴將IPA蒸氣與純水噴向正在旋轉的晶圓上部,同時噴嘴由晶圓中心往外移動。Rotagoni型IPA乾燥是利用晶圓旋轉的離心力與IPA氣體的Marangoni力的乾燥方法。搭載該設備的CMP裝置的概略圖如右圖所示。

## 好厲害! 疏水膜也輕鬆處理!

#### 來實際使用IPA乾燥吧

就像氧化膜是親水性、多矽晶是疏水性,膜質有許多不同的特性。還有些原本是疏水性,但進行CMP後卻改質成親水性。如果是疏水性,使用IPA乾燥是很有效的,但如果是親水性,考量到吞吐量,則使用Spin rinse dry (SRD) 比較好。

這裡我將比較讓裸矽晶圓透過表面處理變成疏水度(親水度)後的SRD與IPA乾燥效果。

#### 那乾燥效果如何?

右圖為裸矽晶圓經SRD及IPA乾燥處理後, 晶圓表面接觸角的缺陷數。一般來說, 晶圓表面疏水度 親水度的特性會以接觸角來表現 在接觸角60度左右的疏水性膜中, IPA製程的缺陷數皆較SRD來得少。而在接觸角30度左右的親水性膜中, SRD與IPA 乾燥的缺陷數則幾乎相同。

依據上述結果,可得知IPA乾燥應用在疏水性膜上可有效減少缺陷。而另一方面,在親水性膜中,我們可以判定SRD與IPA乾燥沒有差異,也就是親水性膜並無乾燥方法的依存性。

#### SRD與IPA

如前所述,依據晶圓表面的條件不同,CMP有可能可以大幅改變表面性質。而我們又希望提升吞吐量。所以我們只要根據表面疏水度來改變IPA乾燥時間就好了。而單晶圓式只要用原本的裝置以SRD就可以達成。只要在SRD加上Rotagoni乾燥,就可以進行IPA與SRD製程。如此一來就可以打造出可依表面特性選擇適當的IPA乾燥,藉以提升吞吐量且又符合環境的裝置。

#### Manabu's Law

在我們這個「研磨與電鍍」的小小技術世界裡,如今也正颳起技術革新的旋風。引領「研磨與電鍍」的人是誰呢?研磨的話,就是因Preston公式而聞名的Frank William Preston博士 (1896-1989)吧。而電鍍的話,就可以追朔到偉大的自然哲學家Michael Faraday (1791-1867)吧。而普雷斯頓與法拉第被日本的愛因斯坦(在說我嗎?)融合了。那就是本書所提出的「廣義與狹義平坦化統一論」。這個理論在半導體晶片永遠的課題—「平坦化」上,提出以製膜技術解決的方法、以削膜技術解決的方法,以及整合兩者的技術。所以研磨與電鍍是Manabu's Law?我這樣說太囂張了對吧(反省)。

半導體業界因摩爾博士與丹納德博士的領導而有今日的景象,3000年前便有的研磨與電鍍技術因普雷斯頓博士與法拉第而科學化。我真的很期待日後會由什麼樣的技術,以及哪位工程師(科學家)來引領業界。Manabu's Law? 覺得捨我其誰的人,請不要害羞,報上名來吧!

162

# 第V篇

**Wet Process Application: Interconnects**

濕式製程應用:多層配線

## 超高樓大廈與多層問題

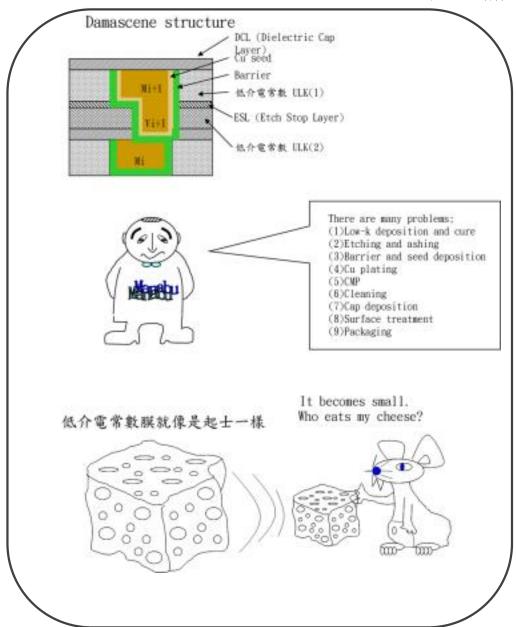

石圖為多層學會時常討論的多層配線問題。就算問題解決了,但隨著世代演進,同樣的問題又會再次出現,簡直就像在玩打地鼠遊戲。不過不要灰心,先努力找出問題的本質吧。開發電鍍與研磨的工程師最好先了解晶片以外製程的問題。

#### 工程師眼中的多層問題是?

電鍍與研磨在晶片製程中應用在: (1) FEOL的STI研磨、(2) 多層配線的鑲嵌用電鍍、研磨、高熔點金屬蓋、凸塊電極電鍍、(3) 封裝上的再配線電鍍等處,但在此我將聚焦在「多層配線」,挑出最近的問題與課題來討論。多層配線製程除了研磨與電鍍以外,還有蝕刻、CVD、PVD、洗淨、退火、灰化、微影(Lithography)等各種製程,但這裡只舉典型鑲嵌構造為例,簡單說明多層問題的基礎。如果讀者是研磨與電鍍的工程師的話,這種程度的問題還是要先瞭解比較好。我是device的門外漢,我想把以下當作是外行人眼中看到的「這就是多層問題的全貌!」來介紹。

#### 鑲嵌構造與其課題

首先簡單介紹多層製程如下。

微影攝影 (Lithography) →低介電常數成膜→膜固化→蝕刻→灰化→阻隔膜成膜→ Cu薄膜成膜→Cu電鍍成膜→洗淨→退火→研磨→洗淨→DCL (Dielectric Cap Layer) 膜或金屬蓋成膜→封裝

發生於各製程的多層問題,我們以下列各製程,一項一項整理來看吧。問題有空洞(孔)、生鏽、傷痕、強度不足等等,就跟公寓或高樓大廈的問題很像。我們來看看細節吧。

這就是多層問題的全貌 Low-k 材料

## Low-k 起司? Low-k 材料

.....

#### 從底部材料銅配線起步

DCL (Dielectric Cap Layer) 是用來當絕緣膜兼Cu的阻隔膜 (Cap)。由於 Dielectric (介電質) 還會採用Co-W等金屬做成Metal Cap Layer,所以有時候也稱 為DBL (Dielectric Barrier Layer)。而對此Layer的規格要求有: (1) 介電常數低、 (2) 有隔離性、 (3) 與底部材料Cu或Low-k的密著性佳。

#### Low-k成膜

先記一下Low-k的種類吧。雖然種類很多,但只要先簡單記一下以下種類就好。

- 將基本的SiO<sub>2</sub> (k= 3.9~4.3) 氟化後, 就會變成SiOF (k= 3.4~3.8)。

- 混合後, k=2.8~3.1

HSQ  $(H - SiO_3)^2 - n$

MSQ  $(CH_3 - SiO_3)^2 - n$

SiOC  $(CH_3 - SiO_3)^2 - n$

- 再進行多孔化, k<2.5

- 若是有機物,則*k*=2.6~3.0

PAE (以產品名舉例的話就是SiLK或FLARE)

- 再進行多孔化後, k<2.5

以這些為基礎知識繼續進行吧。總之,有分為以CVD製作的膜與旋塗 (液體) 製作的膜 兩者的密度 (Dense) 皆約為 $k=2.8\sim3.0$ ,若再經過多孔處理則會變成k<2.5。接著再以H、 $CH_3$ 或分子量更大的 $C_3H_7$ 等元素來取代 $SiO_2$ 的O的話,就能讓構造膨脹,進而造成空洞,並使得k值下降。有了這些概念就足夠了。

所以說, 低介電常數膜看起來就像起司嗎?

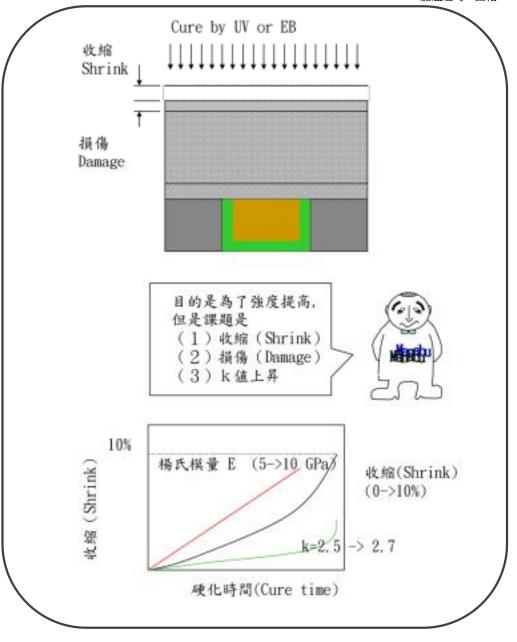

## 加溫起司: 固化

.....

#### Low-k膜的課題

總之, Low-k膜很弱。很弱是什麼意思? Low-k的特性主要以下列六個項目來表示。

- 1) Dielectric constant比 (介電常數): 以*k*表示。

- 2) Young's Modulus (楊氏模量): 以*E* (GPa) 表示, 代表強度。 注)有10GPa左右就很高興了。

- 3) Hardness (硬度): 以*H* (GPa) 表示,代表強度。 注)一般是*E*的20%左右。所以如果*E*=10,則*H*=2GPa。

- 4) CTE (膨脹率): Cu是17ppm, 所以越接近這個值越好。

- 5) Adheresion (密著性): J/m²。一般是5左右,有10以上就很好了。

- 6) 内部應力: Cu是拉, Low-k一般是壓縮。

課題在於如果*k*値下降,*E*也會下降(變弱)。特別是在多孔處理中,原本就是要盡可能地提升空孔率並降低*k*値,所以基本上也會變弱。接下來會說明固化是局部提升空孔率(也就是已經有*k*值變大的覺悟)以提升強度。

#### 固化

UV(紫外線)與EB(電子束)固化的目的是為了提升強度。例如,若固化前楊氏模量£約為5Gpa的Low-k材料,固化後其數值就會上升到10GPa。由於研磨只要有8Gpa以上就好,所以10GPa已經是很棒的數字了。但也不是只有好處。如前所述,固化後膜會收縮(Shrink),導致密度(Dense)增高,介電常數k也會上升。而且表面還會留下傷痕。所以目前固化加工是將k值控制在適當範圍,強度提升同時也控制傷痕。

重點在於膜的收縮。膜在固化時會縮約10%,導致膜累積壓力。且由於密度會增加,*k*值也會上升。進行固化時,就是要抓住適當時機。

起司加溫會縮又變硬?

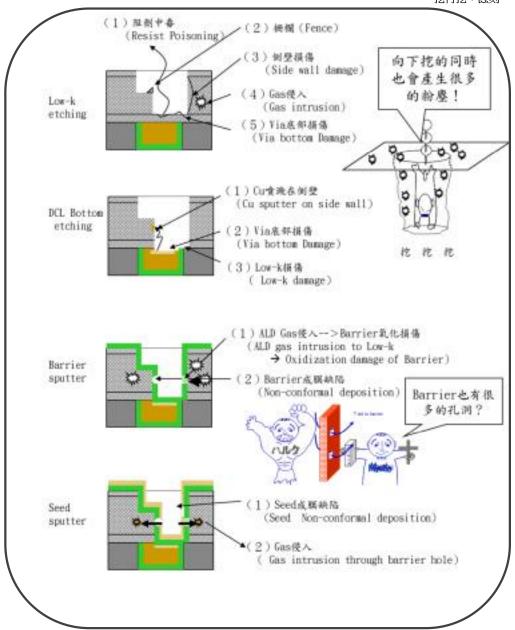

## 一挖再挖: 蝕刻

.....

#### Low-k乾式蝕刻與DCL穿底

乾式蝕刻的課題有好幾個,以下舉出主要幾個。

- (I) N造成的Poisoning: 阻劑中毒 (resist poisoning) 問題。蝕刻的膜若含有N就會產生胺 (NH<sub>3</sub>) , 融化阻劑。這個T-Top現象還曾經一度引起話題。化學增幅型阻劑對N的抗性很弱。

- (2) 對側壁的傷害:有側壁膨脹的Bowing、留下突起的Fence,或壁面平坦度變差,導致之後的阻隔膜包覆性變差等課題。

- (3) Low-k内氣體侵入: 蝕刻氣體, 特別是F跑進Low-k内, 之後與水產生反應變成HF, 並溶在Low-k的問題。

再來是DCL的 (穿底問題):

- (1) Cu飛濺並附著在側壁。

- (2) Cu底受到傷害(氧化等)。

- (3) Cu底凹下。如果是故意打穿 (Punch-through) 的,那倒是沒關係。

- (4) Low-k受到傷害。

#### 阻隔膜(Barrier)與薄膜(seed)成膜的課題

阻隔膜的課題因PVD、CVD、ALD等不同而異。

- (I) 由於PVD無法適型成膜,所以期待就轉向ALD與CVD...

- (2) 但是CVD的純度與密著性差。雖然希望ALD能有所為,但成膜速度與純度也有問題...

- (3) ALD氣體會侵入Low-k, 也有關於BM氧化問題的報告。

- (4) Low-k不平順或阻隔膜周邊成形狀況差,出現缺陷。

薄膜的課題幾乎與阻隔膜相同。

- (1) 薄膜周邊成形狀況差, 需要提升成效。

- (2) 阻隔膜出現的孔與缺陷怎麼處理? 可以100%修補嗎?

目前的目標是讓阻隔膜盡量薄但同時又維持防止擴散功能,目前已達到5nm級距。且已經有發表說未來會達到2nm。薄膜也是以5nm以下為目標。這麼薄的膜有可能完美地進行成膜嗎?底部材料的Low-k膜已經亂七八糟了,還要在上面塗東西?

這就是多層問題的全貌

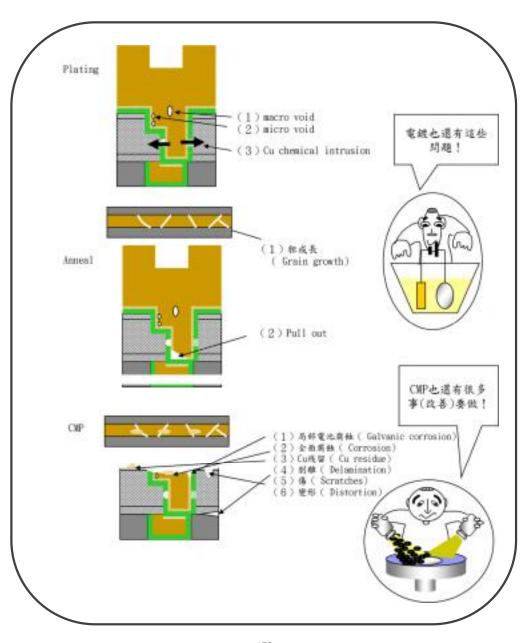

## 電鍍與CMP也有問題

.....

#### 電鍍與退火的課題

以下只舉出電鍍的主要課題。

- (1) Cu液侵入:如果阻隔膜做得不好,液體就會侵入。曾經還有人說過Cu離子會通過阻隔膜侵入Low-k。怎麼可能?哪有這種Cu離子。那是因為原本阻隔膜或薄膜就已經有孔(缺陷)了,所以才會侵入。所以簡單來說,問題在於如何製造出無缺陷的阻隔膜與薄膜?要解決這個問題就必須一併解決前一製程的蝕刻表面粗糙問題。

- (2) Void: Void有Macro與Micro Void。Micro會成為之後EM與SM的問題。Macro的Void 雖然不再討論範圍內,但Cu薄膜面上的Micro Void當然也是個問題。其他問題還有晶粒界面上更小的奈米Void。這奈米Void平常看不到。但在加工DCL並進行熱循環之後,就會不知道從哪裡跑出來聚集成大Void,也就是所謂的SIV(Stress Induced Void)。Cu在成膜時有拉伸應力,但加熱時則會收縮。Cu的應力會因為熱循環與當時周邊DCL的CTE之差而變小或變大。此時這個奈米Void就會移動。

- (3) 電鍍液的純度、EM與SM: 電鍍還有許多待解決的問題。目前電鍍液是不純物越多越有SM耐性,但這不是根本的解決方法。使用不純物少的電解液,達到EM、SM與Void都少的目標才算解決問題。

#### 退火的課題

- (1) 退火時的粒徑成長控制是一種技術。粒徑越大,對Scattering問題也比較好。

- (2) Pull Out:以前退火如果處理不好,通孔(Via)底部會穿孔。雖然現在已經解決這個問題,但可以確定的是應力還是會潛在性地增高吧。

#### CMP的課題

僅列舉研磨的主要課題如下。

(1) 電偶腐蝕 (Galvanic corrosion) 、 (2) 全面腐蝕、 (3) Cu殘留、 (4) 剝離、 (5) 傷痕、 (6) 變形。

這就是多層問題的全貌 漏電!沒辦法安心居住:可靠性!

## 漏電!沒辦法安心居住:可靠性

.....

#### 表面處理的課題

表面處理方面有研磨後的洗淨、乾燥與DBL成膜前的電漿處理。研磨後的洗淨與乾燥是在Cu表面稍微留下一點氧化膜或Cu(錯合物),在等待時間內在不腐蝕的狀況下加工。此外,Low-k膜則要洗淨與乾燥,使Cu、CuOx與Cu錯化物不殘留。此處理的最大問題在就在於水痕(watermark)。

關於DBL成膜前的電漿處理有許多報告。基本上是以NH3、H2或He等氣體的電漿進行處理, 所以雖然可以達到洗淨目的,但當然也會留下損傷。而損傷容許範圍是多少,那就是技術了。

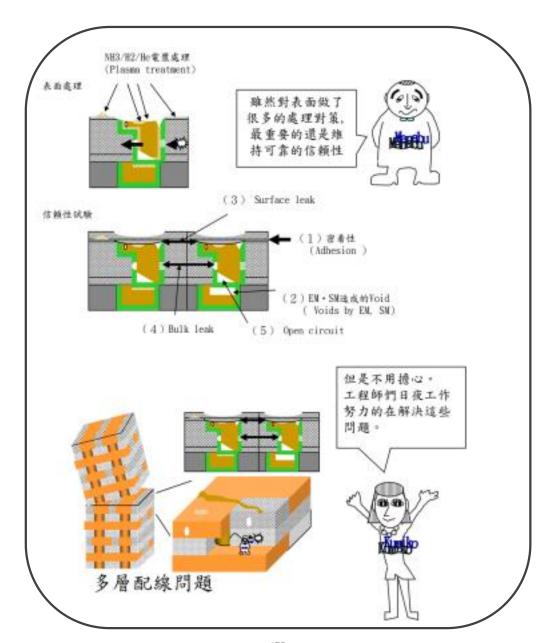

#### 可靠性評估

因為上述問題, 因此有了可靠性評估。如圖所示, 大致來說有以下代表性的五項。

- (1) DCL的密著性: 想以表面電漿處理等方法提升密著性, 大概會到10J/m²左右。

- (2) Cu表面變質: 結果導致EM與SM變差。

- (3) Surface leak: 表面洗淨不夠確實、Low-k受到損傷。

- (4) Bulk leak: 發生阻隔膜不完美、DM氧化或劣化。

- (5) Open (因Void造成): 又是電鍍造成的, Void與表面缺陷仍多。

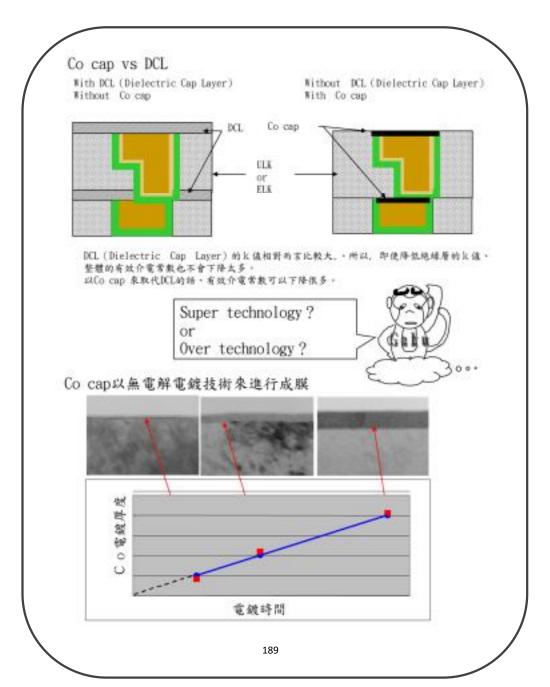

#### 金屬蓋的課題

Co-W等金屬蓋仍有許多問題。而由於EM已經改善,因此有朝一日很有可能成為獲得運用的技術。

#### 封裝的課題

黏合 (bonding) 之際的應力分析為主要項目。必須進行 (I) Wire Pull、 (2) 熱循環、 (3) 剪應力等應力分析。

Seven See's 七個課題與七個解法

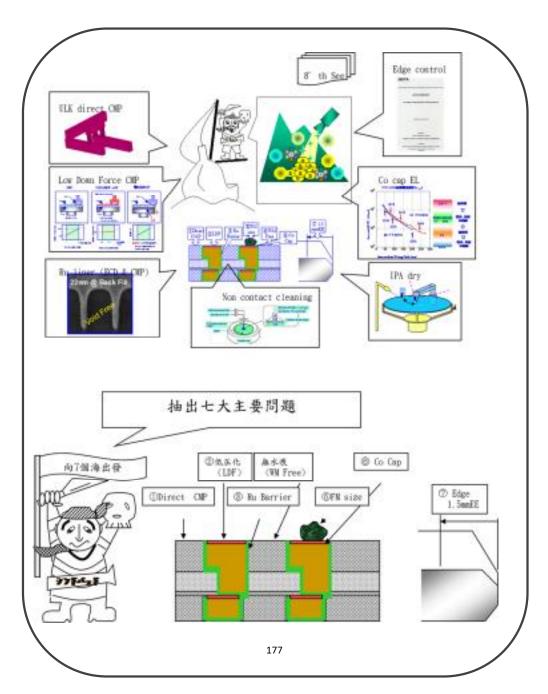

## 七個課題與七個解法

.....

#### 什麽是Seven See's?

一路說明多層配線的問題到此,已經掌握到哪裡有問題了。那麼這章節就提出解決方法吧。我從User roadmap (含ITRS) 抽出七大課題來介紹。Seven See's意涵著七個發現,這些開發與解決方案包含著太多風險,所以用辛巴達的七海冒險來比喻。

#### 來自roadmap的要求

以下為從各公司的roadmap推估的七個發現See與有望提供解決方案的技術。

1'st See: Low-k層的直接CMP (Direct CMP) →

多孔Low-k (k=2.5) 膜的直接研磨課題。

2'nd See: 低壓化要求 (Low Down Force Planarization)

解決數年前就出現的低壓問題會要求到什麼地步的問題。

3'rd See: 釕阻隔膜 (Ru Barrier Application)

是否採用45nm世代仍在觀望的Ru阻隔膜(或薄膜)?

4'th See: 無水痕 (Water Mark free)

與1的Direct CMP有關,k=2.5的疏水膜洗淨乾燥。

5'th See: 雜質大小CD (Critical Dimension) 的1/2 (Small FM Size of 1/2 CD)

CD變小, 缺陷大小要管理到什麼地步的問題。

6'th See: 金屬蓋 (Co Metal Cap)

作為對增加的Jmax提升EM的手段。

7'th See: 邊緣排除 (Edge Exclusion to 1.5 mm)

上述的七個課題很重要。這是65nm世代需思考的課題,但對45nm世代、32nm 以後的世代來說仍依然是重要課題,須好好地處理。

## 1'st See Direct CMP

.....

#### Direct CMP要求是什麼?

目前有在研究的多層配線鑲嵌模組整合有以下三種。

·情況1:無HM (硬遮罩, Hard Mask), 配線與通孔介電常數相同。

·情況2:有HM,配線與通孔介電常數相同。

·情況3:有HM,配線與通孔介電常數不同。

其中情況1就是Low-k膜的Direct CMP。

#### 問題與對策例

問題是什麼?

在情況1中,需要擔心RIE造成的損傷與CMP造成的損傷。為此必須開發損傷少的低介電常數膜,以及修復損傷的技術。

在情況2與3中,雖然無法避免RIE造成的損傷,但CMP造成的損傷會由HM擋住,所以比情況1安全。使用低介電常數材的目的是降低RC中的C,整合的有效介電常數 Keff是問題所在。各公司是在比較過生產技術(確保可靠性)與設計要求Keff後,再決定是要選擇採用上述哪個情況。此時勝負關鍵就在於能把HM做到多薄。

右圖是變動範圍在±5nm與±10nm時的RC變動。

如何降低這個變動是微細化最新的課題。在圖的例子中,是透過採用Closed Loop Control進行渦電流監測之舉,達到抑制此一變動。

這個Direct CMP問題早在SiLK這種有機膜問世以來,就一直是個問題。想降低有效介電常數,但又會有對有機膜造成極大損傷。那是不是要設置硬遮罩?這就是工程師的煩惱。結果,最後應該會隨著CMP和修復技術的改善與開發,出現許多挑戰與妥協吧。

Direct CMP 的挑戰仍將繼續持續下去。

Three cased of intergration CIP均一性 CMP+0 -- Ht. Direct 是重要的 CVP THomogeneous \$2 ②用vbrid型 THomogeneous \$2 (没有BM) (表田() (A/HA) CMP的均一性對RC所造成的影響很大 CIP均一任 是重要的 K-3, 0.86 in 厚度與均一性 10 BCet吸化本[%] (max-min)/ave K-3. 0 K-2.3 K=2.5 ±50m ±10nm HR 加工特度 [mm] 渦電流 monitor 變得很重要 我好精度的邓点检出 \*\* 東联:Cu / W Title US Patent IN-SITU MONITORING OF THE 5, 559, 428 CHANGE IN THICKNESS OF FILMS IN-SITU MONITORING OF THE CHANGE IN 海電 Monitor 5, 731, 697 THICKNESS OF FILMS 179

1'st See Direct CMP

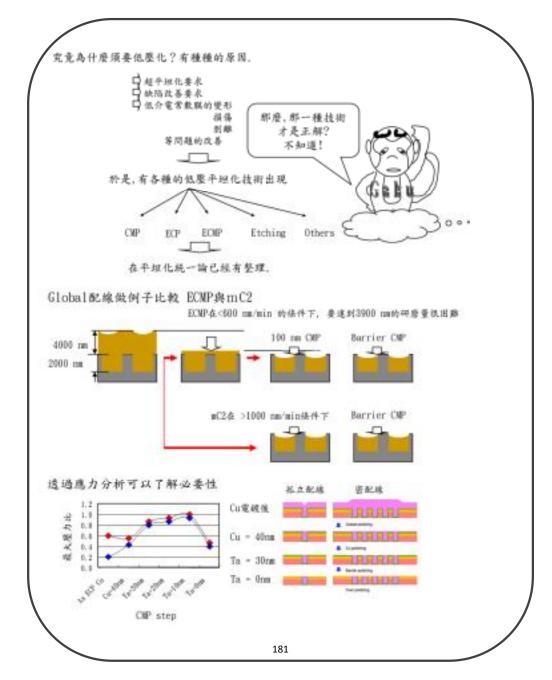

## 2'nd See: CMP低壓化要求: mC2是什麼?

.....

#### CMP低壓化要求 (Low Down Force) 是什麼

以前之所以會出現低壓化要求,是因為Low-k材料強度太弱,會在CMP的加壓研磨過程中被破壞。而其基準就是Low-k材料的楊氏模量E,當時(我記得最剛開始是出現在Sematach的報告中)是提出要 10 GPa以上,所以固化的基準就變成了10 GPa。再接下來是剝離。而其基準就是密著性,這方面尚未設定明確的基準值。目前是使用破壞力學中的Gc值或四點彎曲法等實驗數據。對此,有人提出了首先應該先達成CMP研磨低壓化的意見。當初的低壓力要求值是0.5psi以下,因而出現電解研磨,但CoC(Cost of Consumable)也成了問題,目前雖然說是低壓力,但會隨著不同使用目的而將其數值控制在1~3psi之間。

#### 對策例

詳細內容請參照平坦化統一論。該段文章介紹廣為各界應用的CMR、ECR、ECMR、CE等各種低壓削膜技術,統一說明其原理,並介紹其實CMP與ECMP是相同的技術,世界上還有融合蝕刻的研磨方法(mC2)。因此,使用者應該會考慮CoC,決定適合自己的系統吧。

#### ECMP對mC2

右圖以Local配線和Global配線範例比較兩者。圖中比較使用複合電解研磨 (ECMP) 時與使用化學性高的mC2 (CEP: Chemical Enhance Polish的一部分) 進行研磨的差異。要採用哪一種,使用者會在考量CoC過後決定。

結論就是使用者應考慮過CoC後再做決定,只要在1.5~3psi之間選擇適當的數值就好。

Seven See's 3'rd See 釘阻隔膜

## 3'rd See 釕(Ru)阻隔膜

.....

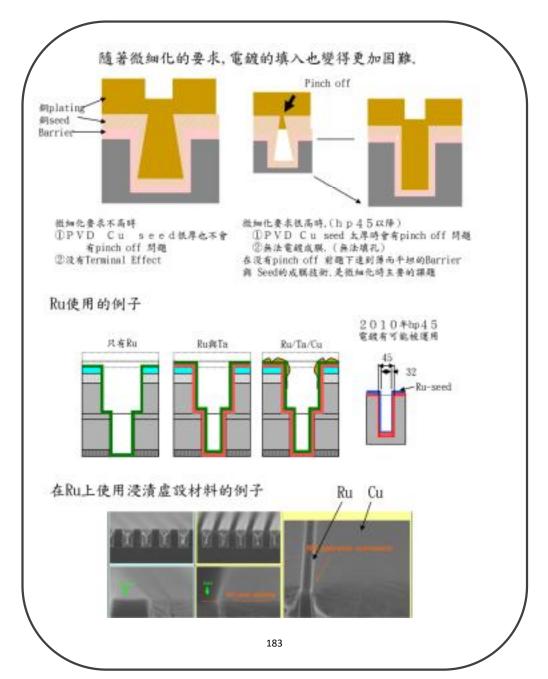

#### 什麼是薄膜與適型阻隔膜?

在ITRS中雖然只有簡單談到新的材料,但阻隔膜薄膜化的這個目標卻已經非常明顯。為達到降低RC的目標,阻隔膜就一定要薄膜化。這在過去的PVD中,已經是個很難搞的問題,幾年前開始又在CVD(ALD也是CVD的一種)中再次出現。這是因為除了利用CVD製作薄又適型的膜以外,沒有其他的解決方案。最近PVD也出現成膜後再重濺鍍(Resputter)等適型成膜技術。而Ru就是在這其中出現的候選新材料。

#### 課題是什麼?

薄化Cu薄膜就會使抗阻變高,電鍍的Terminal Effect<sup>注)</sup>也會變明顯,成模便會 因而不均。針對此問題,目前是以虛設電阻與分割陽極等方法來改善。

除了薄化Cu薄膜以外,目前也已經出現在Ru上直接電鍍成膜的需求。

注)指因晶圓中央比端部的抗阻高,導致端部的電鍍厚度變得較厚的現象。

#### 對策例

右圖為在Ru上使用浸漬虛設材料的電鍍方法來成膜的例子。考量到往後晶片薄膜化的需求與提升可靠性的目標,Ru應也是優良的候選材料之一。

雖說是Ru用的CMP,但目前還沒有人真的認真開發Ru用CMP磨液。如果Ru實際 獲得採用的話,磨液的開發應該也會有快速進展吧。

Seven See's 4' th See:無水痕要求

## 4' th See: 無水痕要求

.....

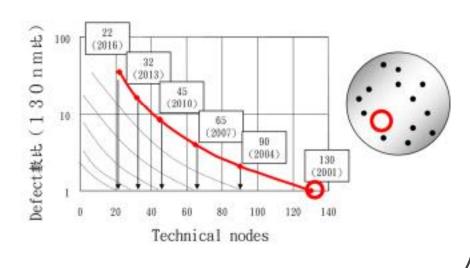

#### 水痕WM「0」

水痕(water mark, WM)就是「0」,是完全不允許存在的。WM是指以SiH<sub>x</sub>O<sub>y</sub>型態出現的「水玻璃」。Si面上如果有水,Si與空氣中的氧就會溶入水中,形成SiH<sub>x</sub>O<sub>y</sub>。將其乾燥後,水會飛散,而SiH<sub>x</sub>O<sub>y</sub>會凝縮成像「肚臍」的東西,也就是所謂的水痕。親水膜(TEOS)不會有水痕產生。疏水膜(ULK)則容易產生水痕。要避免這個問題,最有效的方法是IPA乾燥。由於IPA是將水以其他東西代替,所以不容易產生水玻璃。右圖為TEOS、ULK與ULK疏水度的差異。疏水度不同,水的接觸角也不同,且乾燥後的水痕與疏水度成正比,數量變多。

#### 對策例

以下介紹Rotagoni乾燥的一例。

Rotagoni乾燥是IMEC開發的技術,將Marangoni效果開發成單晶圓設備,並具有吞吐量上的優越性。此技術將IPA與純水導入晶圓,並同時旋轉晶圓使其乾燥。

由於Rotagoni乾燥也用來當作無IPA的Spin dry乾燥(SRD),因此可配合膜的疏水度改變IPA效果。右圖表示當疏水度高時,就必須「花時間慢慢」乾燥,而當疏水度低時(接近親水)則可快速乾燥的例子。其目的在於盡快完成乾燥以提高吞吐量。順帶一提 Flash用的多矽晶在研磨後親水性會增加,即使使用SRD也能獲得良好結果。日後應考量膜的表面在研磨與洗淨後的疏水度,再決定IPA的乾燥時間,藉此開發CoC少且環保的乾燥方法。

Seven See's 5'th See:1/2CD雜質大小

## 5'th See: 1/2CD雜質大小

.....

#### 1/2CD雜質大小的要求是什麼?

ITRS要求如右圖所示,雖然隨著微細化的發展,缺陷 (Defect) 的容許大小值越來越小,但實際大小受限於測量儀器的極限。目前光 (UV光) 只能正確測量到約100nm (0.1µm)。測量儀器製造商雖然已經提出預定製造45nm或32nm的產品藍圖,但UV光的波長是193nm,就理論上來說,研判1/2波長的100nm大概就是極限了。當然如果能應用各種改善技術來達到45nm或32nm的話,那就太令人興奮了。

那麼「看不到的雜質 (FM)」要怎麼管理?其中一個方法是用統計學。只要應用無塵室的FM與其大小的2~3倍成反比的法則,即可逐漸降低可測量大小的FM規定值。不管如何,這牽扯到良率,應該與晶片製造商一起思考簡單且可靠的品質管理方法。

#### 對策例

先來講跟洗淨有關的改善技術。在45nm以後的洗淨中,缺陷很難分辨到底是損傷還是雜質。所以採用非接觸式洗淨,避免在洗淨時造成損傷是很重要的。